## Design and Development of a One Gigasample per Second Radar Data Acquisition System

## Ryan Kelly Eakin

B.S.E.E., University of Kansas, 1999

Submitted to the

Department of Electrical Engineering and Computer Science

and the Faculty of the Graduate School of

the University of Kansas

in partial fulfillment of the requirements for the degree of

Master of Science.

| Professor in Charge   |

|-----------------------|

|                       |

|                       |

|                       |

|                       |

| Committee Members     |

|                       |

|                       |

| Date Thesis Presented |

## **ACKNOWLEDGEMENTS**

I would like to thank God for blessing me with a wonderful family who sacrificed so much to make this degree possible. Thanks to Dr. Allen and Dr. Gogineni for allowing me to work on such a challenging project. The experience has been irreplaceable and played a key role in landing my current job.

#### **ABSTRACT**

To more accurately determine the role of glacier ice systems in sea level rise, glacier accumulation rate measurements are needed. This information has traditionally been gathered using core samples resulting in a measurement error exceeding 20 percent when sparse measurements are extrapolated over the entire ice sheet. To improve temporal and spatial accuracy of these measurements, the University of Kansas Radar and Remote Sensing Laboratory is developing a wideband, 600- to 900-MHz pulse compression airborne accumulation radar system. This thesis presents a 1 Gsample/sec radar data acquisition system developed for this accumulation radar. The system has the ability to digitize signals with bandwidth as high as 500-MHz and frequencies as high as 2.2 GHz. A special digital timing system is also presented which provides precision timing signals to the acquisition system as well as general timing for the entire radar. The analog to digital conversion section of the system was shown to operate at 1 Gsample/sec with an input up to 2.2 GHz as stated in the manufacturers datasheet. The timing system was shown to operate up to 2.4 GHz. The entire acquisition system could not be completed because one card in the system could not be made to work properly due to manufacturability issue. The logical design of this card has been shown to be correct and the system could be completed with a revision of this one board.

## **Table of Contents**

| CHAP      | TER 1 INTRODUCTION                                                   | 1   |

|-----------|----------------------------------------------------------------------|-----|

| СНАР      | TER 2 THEORY AND CONCEPTS                                            | 4   |

| 2-1       | Nyquist Sampling Theorem Review                                      | 4   |

| 2-2       | Limitations and Characteristics of Real Analog-to-Digital Converters | 7   |

| 2-3       | Interleaving of Analog-to-Digital Converters                         |     |

| 2-4       | Coherent Averaging of Radar Signals                                  |     |

| CHAP      | TER 3 DATA ACQUISITION SYSTEM DESCRIPTION                            | 15  |

| 3-1       | System Overview                                                      | 15  |

| 3-2       | Analog to Digital Converter Card                                     |     |

| Ov        | verview                                                              |     |

|           | etailed Description                                                  |     |

| Re        | evision History/Future                                               |     |

| 3-3       | Averaging Card                                                       |     |

|           | verview                                                              |     |

|           | etailed Descriptionveraging Card PCB                                 |     |

|           | SP Programming                                                       |     |

|           | evision History/Future                                               |     |

| 3-4       | Multiplexer Card                                                     | 65  |

|           | verview                                                              |     |

|           | etailed Description                                                  |     |

| Re        | evision History/Future                                               | 77  |

| 3-5       | Computer Interface                                                   |     |

| CHAP      | TER 4 TIMING SYSTEM DESCRIPTION                                      | 83  |

| 4-1       | Universal Timing System Overview                                     | 83  |

| 4-2       | Timing System Mezzanine Card                                         | 88  |

|           | verview                                                              |     |

|           | etailed Description                                                  |     |

| Ke        | evision History/Future                                               |     |

| 4-3       | Timing System Main Card                                              |     |

|           | verview                                                              |     |

|           | etailed Descriptionevision History/Future                            |     |

|           | •                                                                    |     |

| 4-4<br>De | Timing System Microcontrollerescription                              |     |

| CHAP      | TER 5 SPECIAL TEST AND MEASUREMENT DEVICES                           | 129 |

| 5-1       | ECL-to-Sine Wave Converter                                           | 129 |

| 5-2       | ADC Card Test Circuit                                                | 131 |

| 5-3   | Avera    | ging Card Test Circuit           | 134 |

|-------|----------|----------------------------------|-----|

| 5-4   | Other    | Special Equipment                | 136 |

|       | L/PECL   | Coaxial Terminators              | 136 |

| Hig   | gh Speed | l Oscilloscope                   | 137 |

| СНАРТ | ER 6     | MEASUREMENTS                     | 139 |

| 6-1   | Timing   | g System Measurements            | 139 |

| 6-2   | ADC (    | Card Measurements                | 140 |

| 6-3   | Averag   | ging Card Measurements           | 143 |

| 6-4   | Acquis   | sition System Measurements       | 144 |

| СНАРТ | ER 7     | CONCLUSIONS AND RECOMMENDATIONS  | 147 |

| REFER | ENCES    | 5                                | 150 |

| APPEN | DIX A    | ADC CARD SCHEMATICS              | 151 |

| APPEN | DIX B    | AVERAGING CARD SCHEMATICS        | 161 |

| APPEN | DIX C    | MULTIPLEXER CARD SCHEMATICS      | 181 |

| APPEN | DIX D    | TIMING MEZZANINE CARD SCHEMATICS | 187 |

| APPEN | DIX E    | TIMING MAIN CARD SCHEMATICS      | 201 |

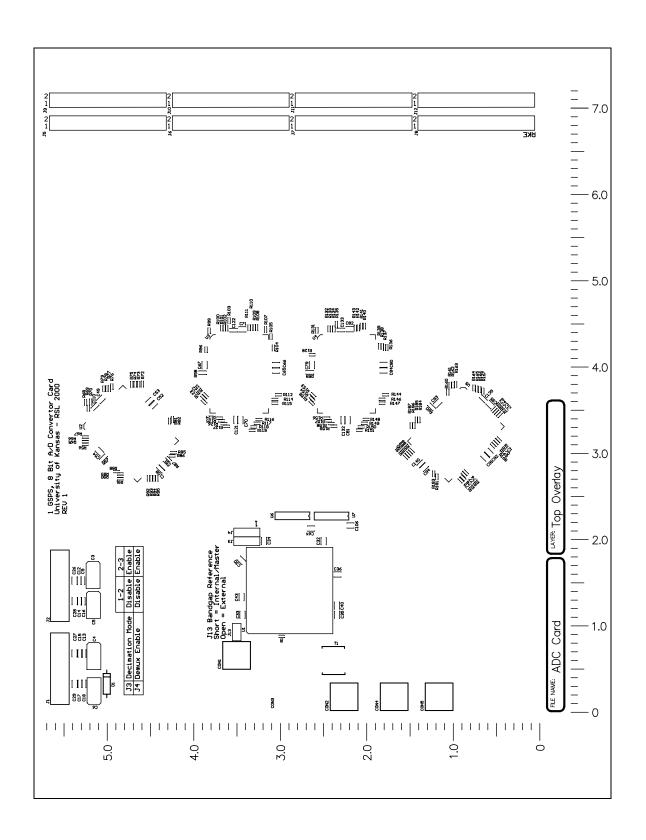

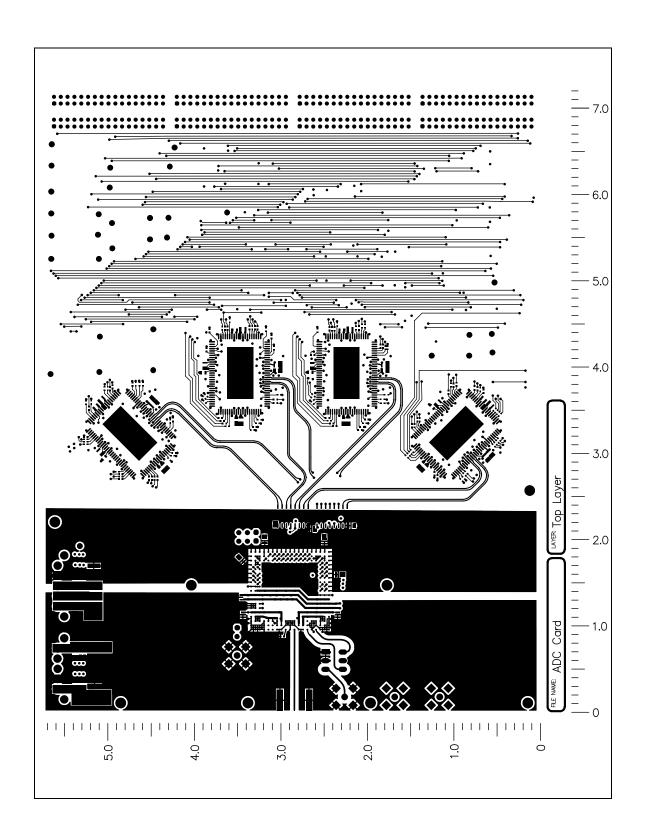

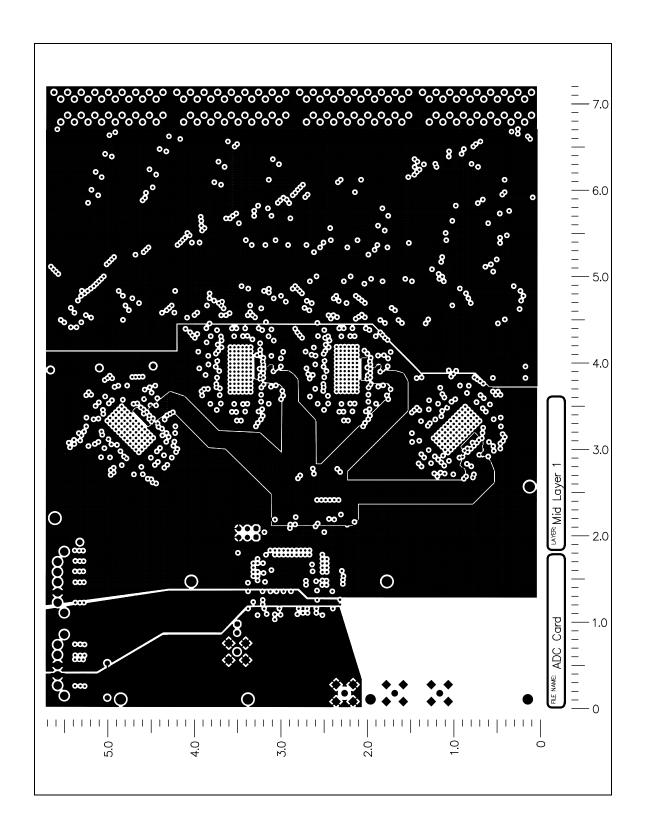

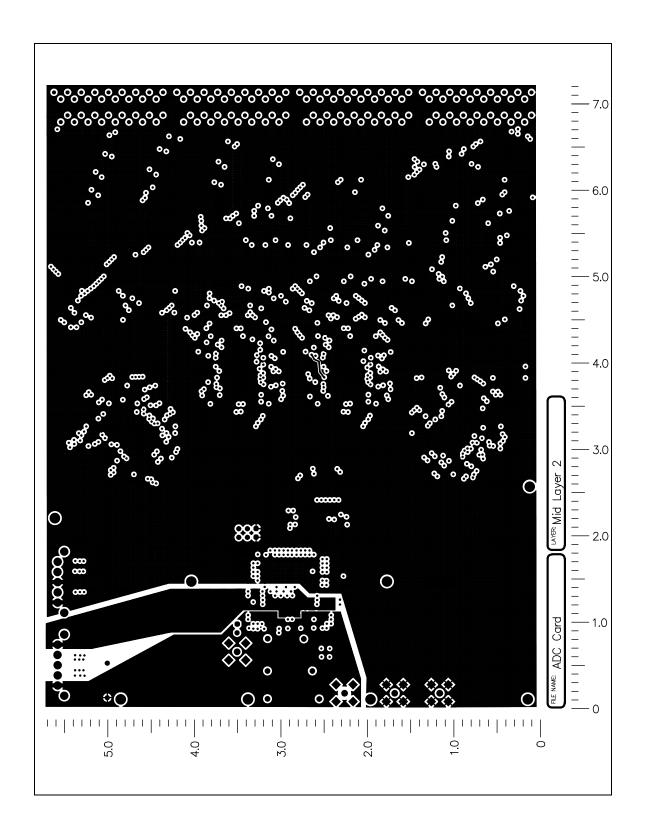

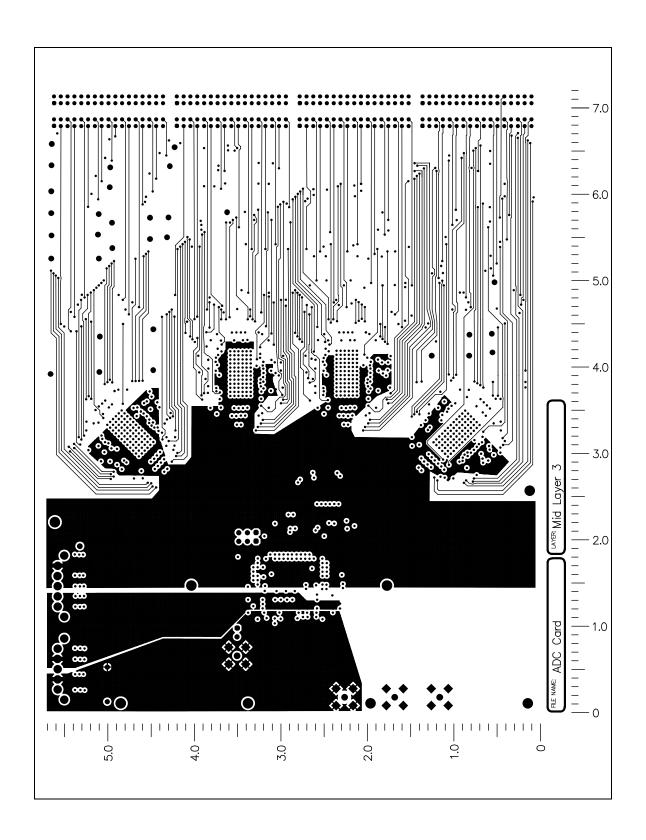

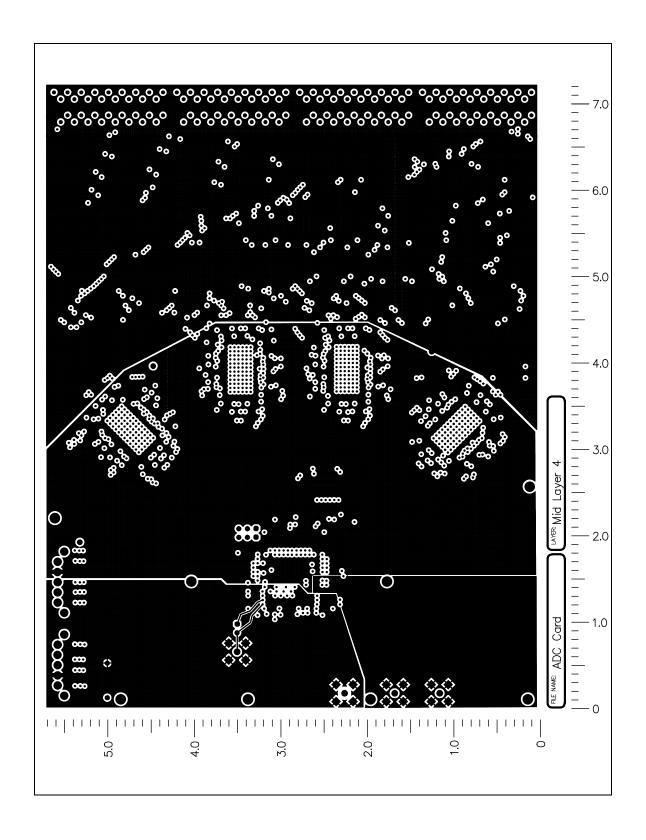

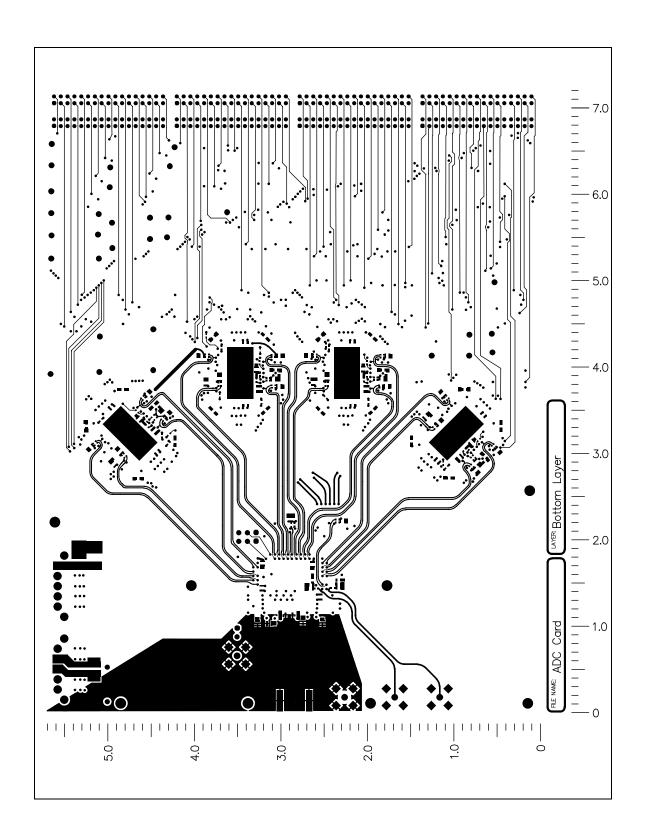

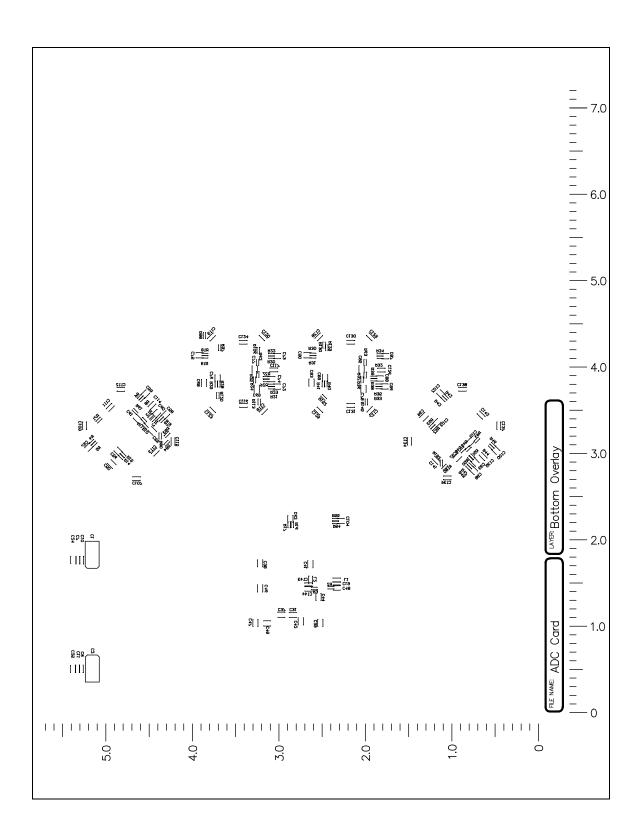

| APPEN | DIX F    | ADC CARD PCB LAYOUT              | 246 |

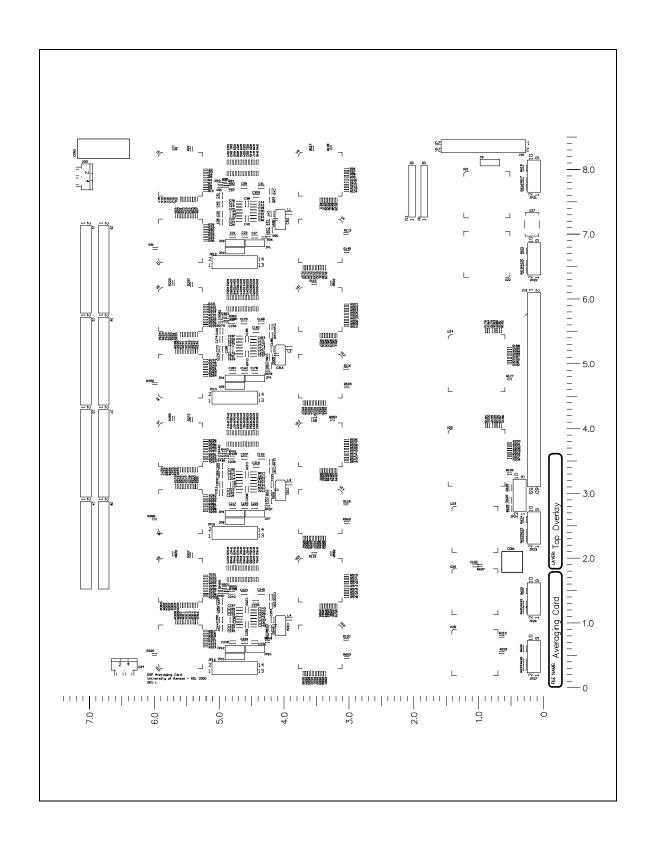

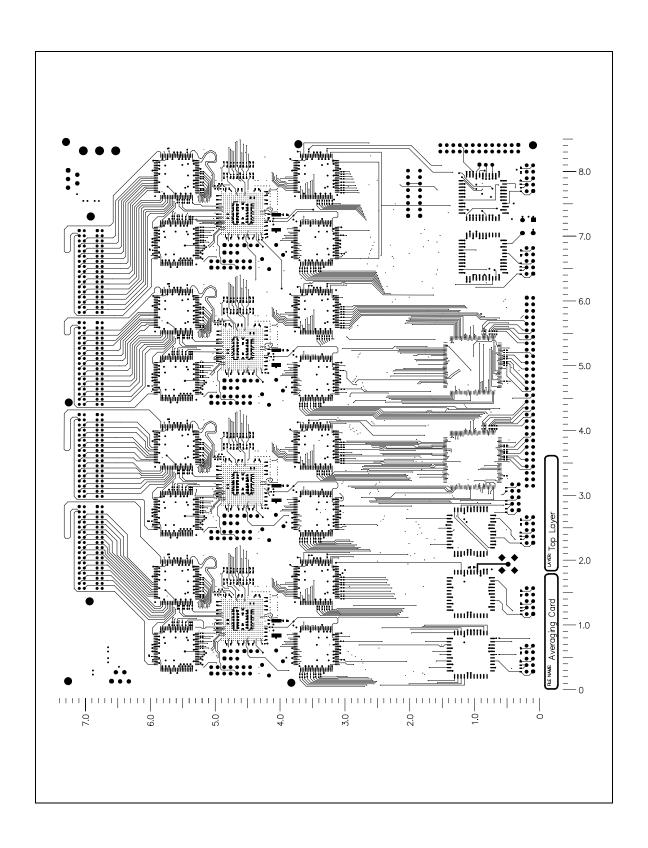

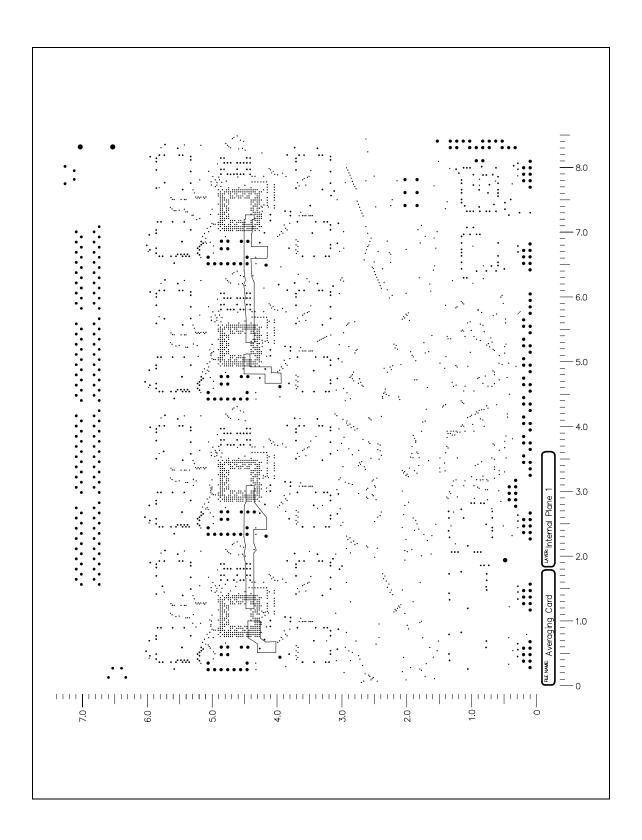

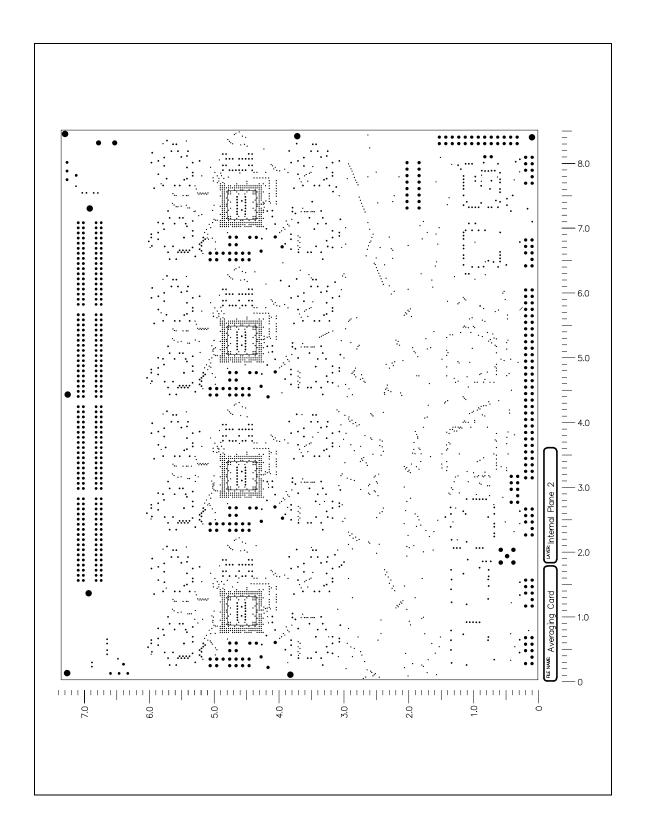

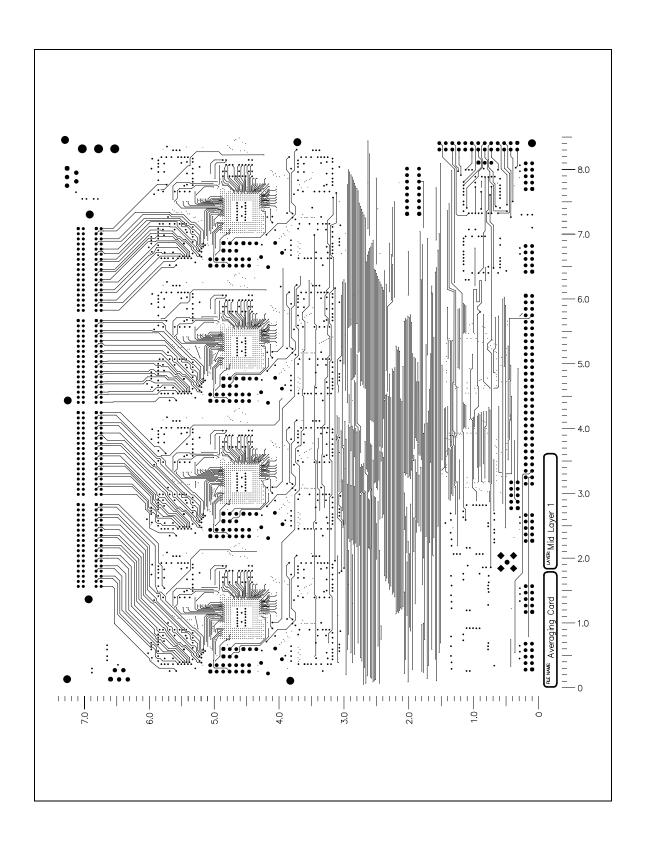

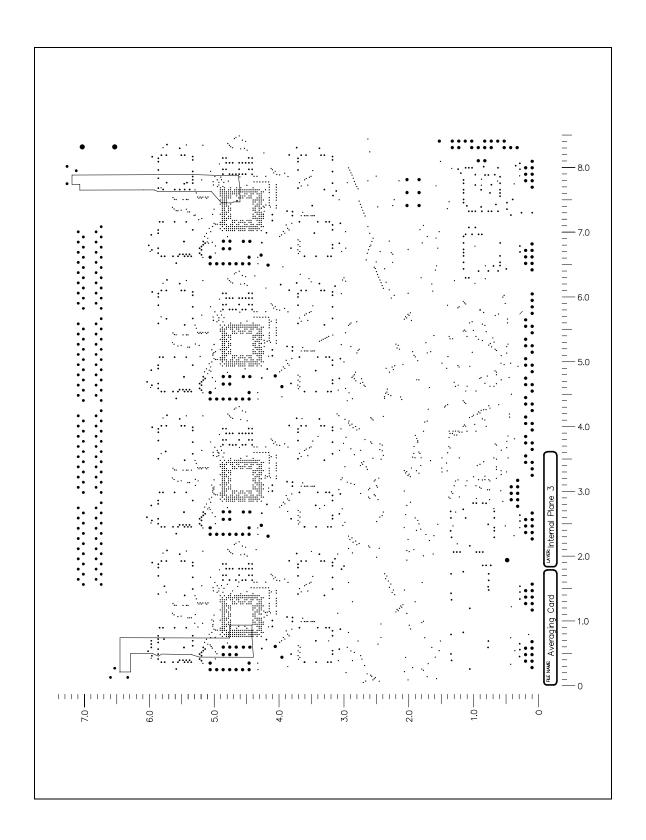

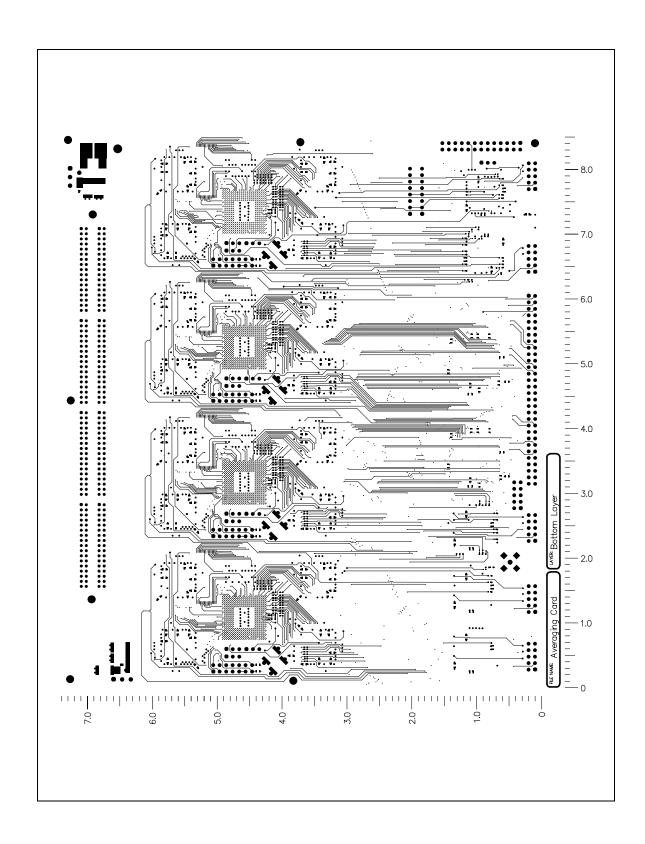

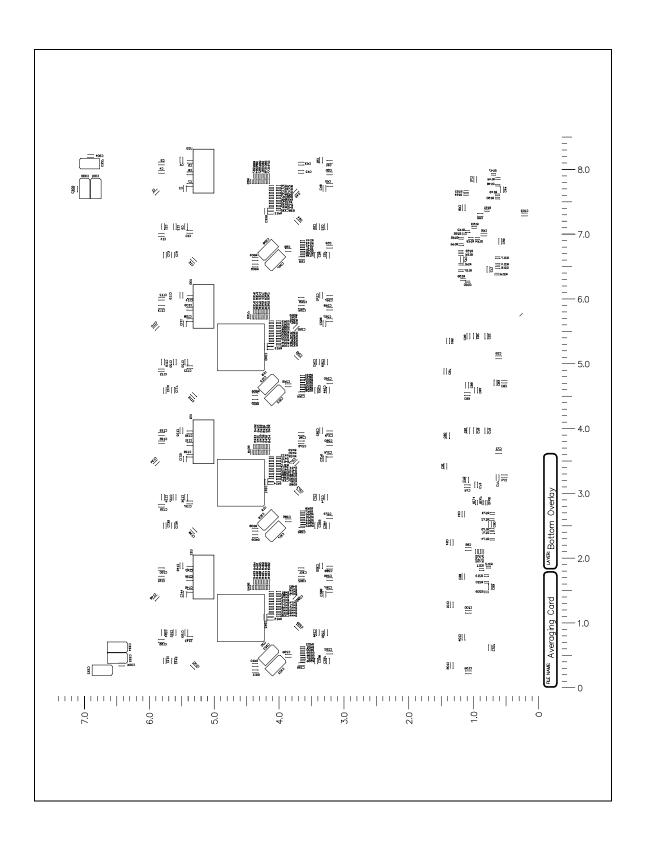

| APPEN | DIX G    | AVERAGING CARD PCB LAYOUT        | 255 |

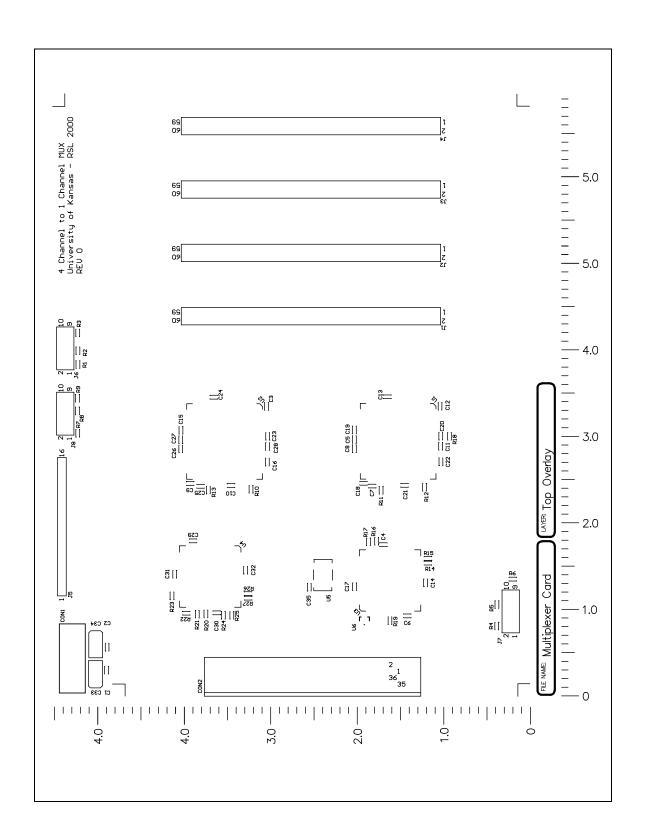

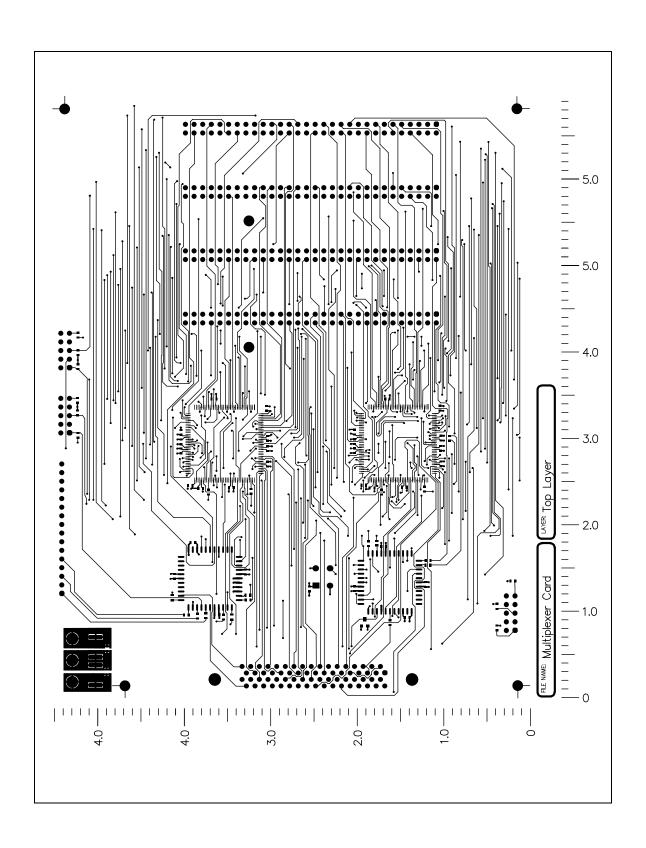

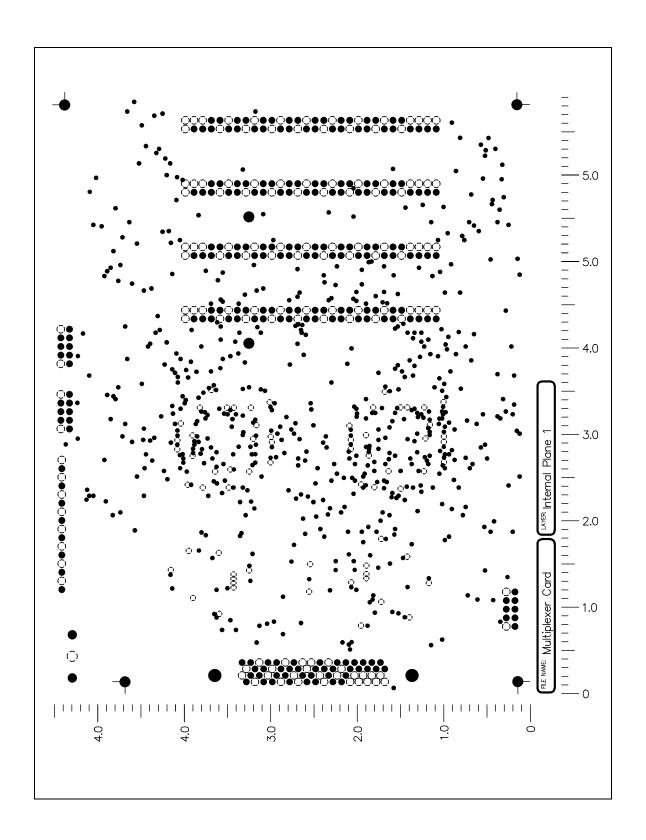

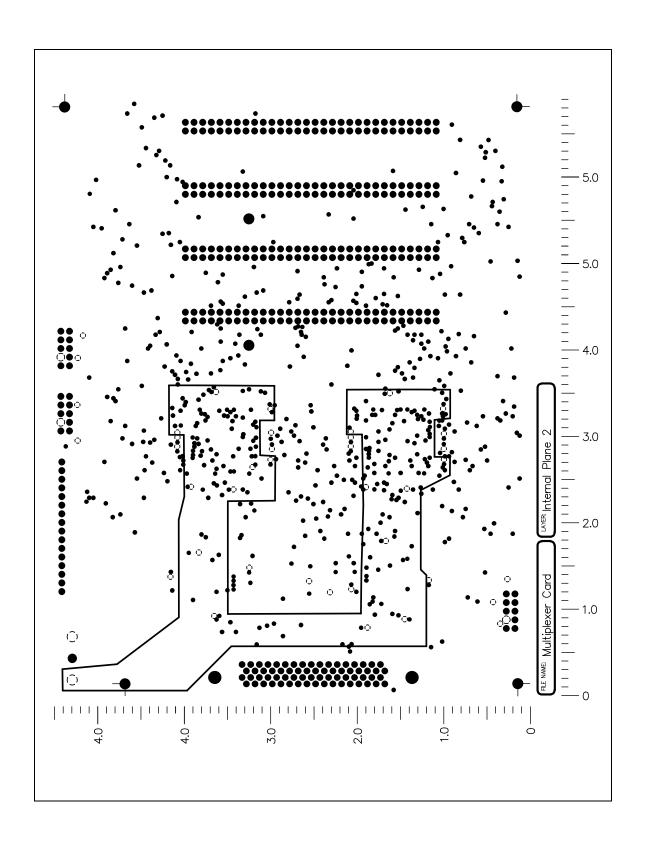

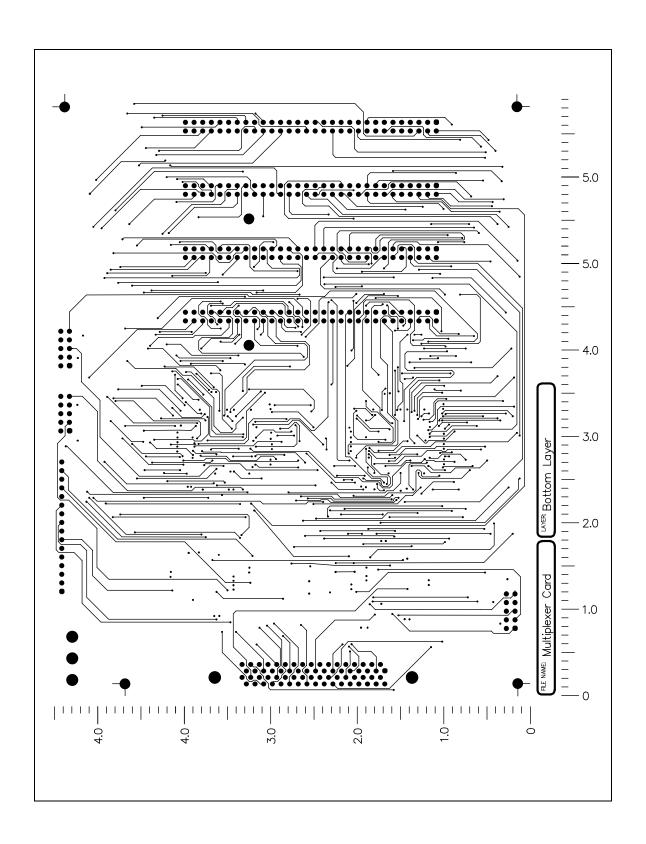

| APPEN | DIX H    | MULTIPLEXER CARD PCB LAYOUT      | 264 |

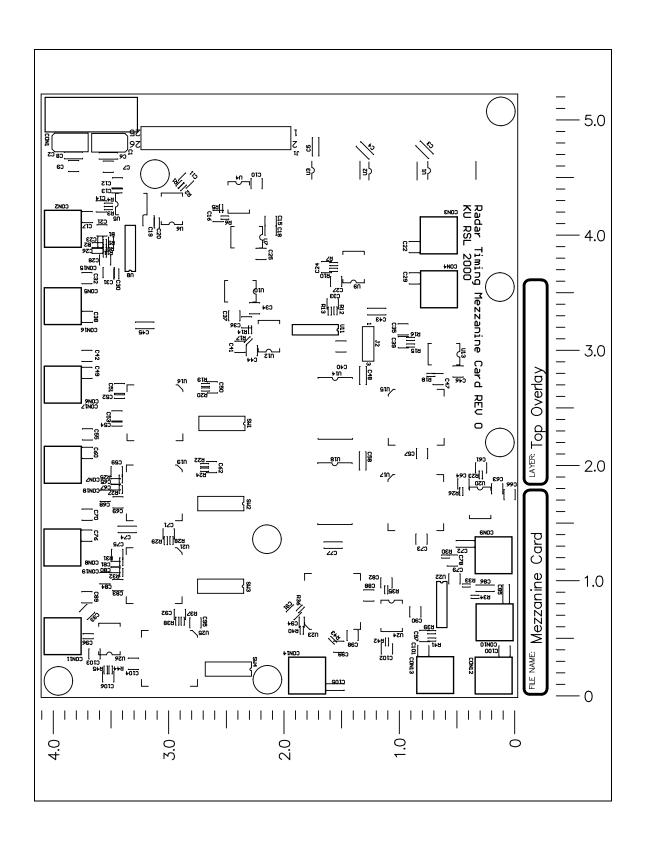

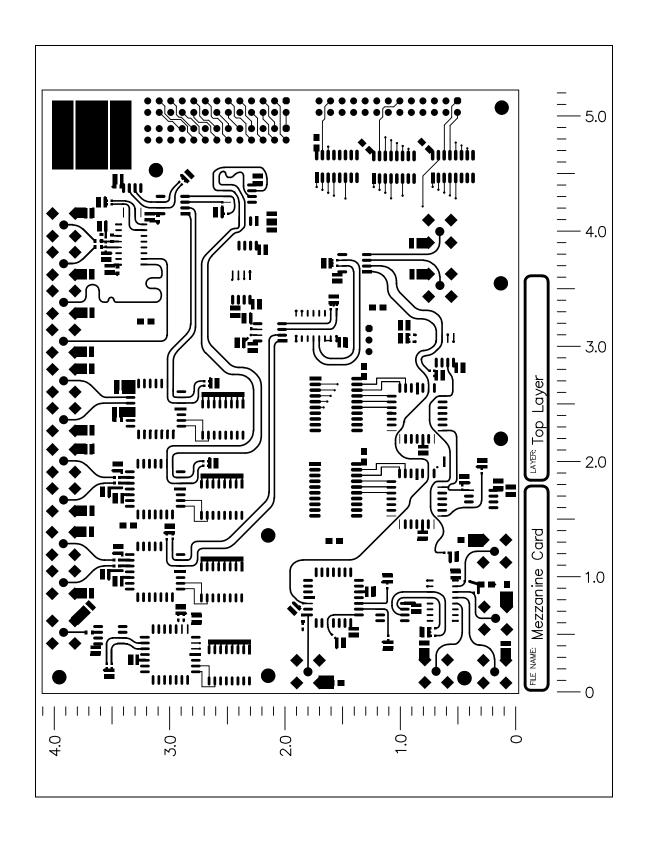

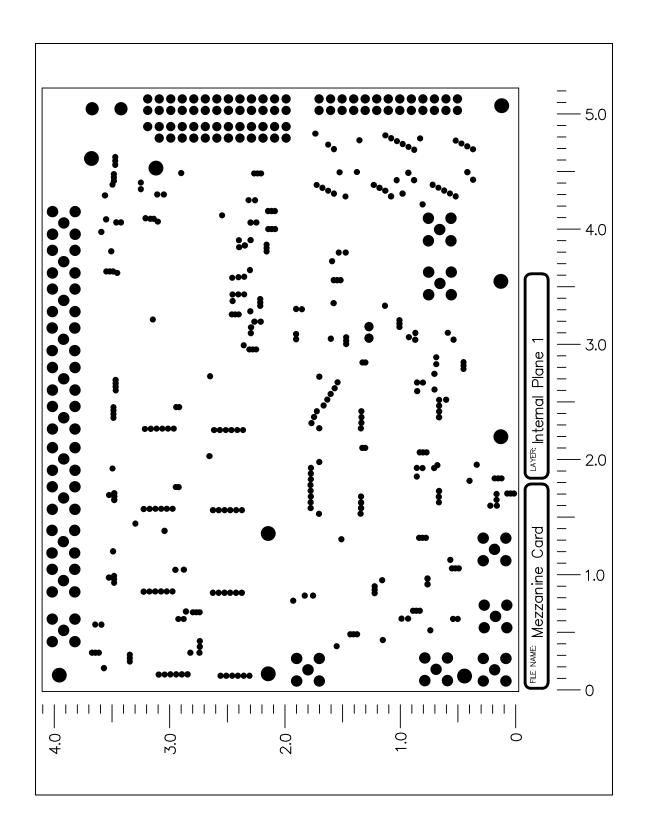

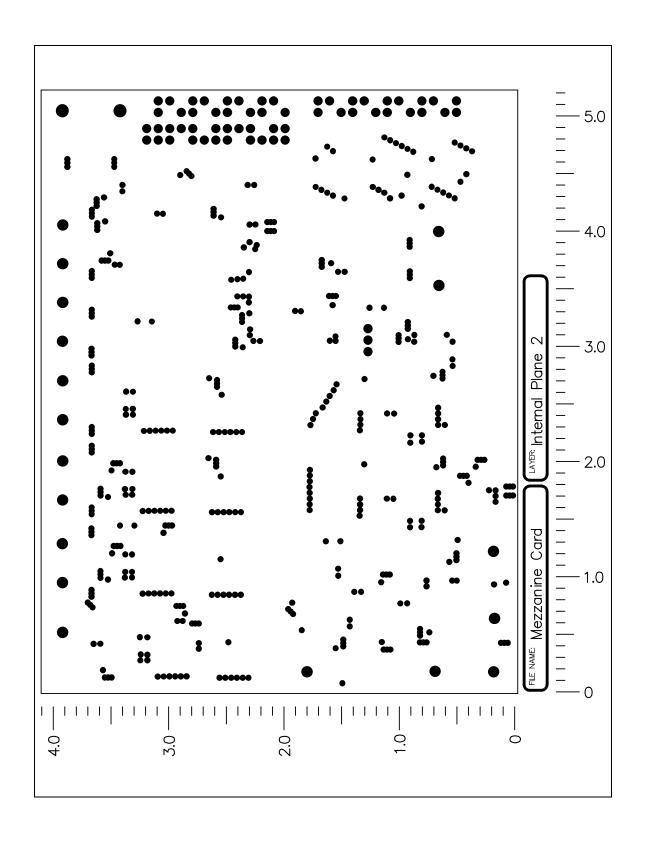

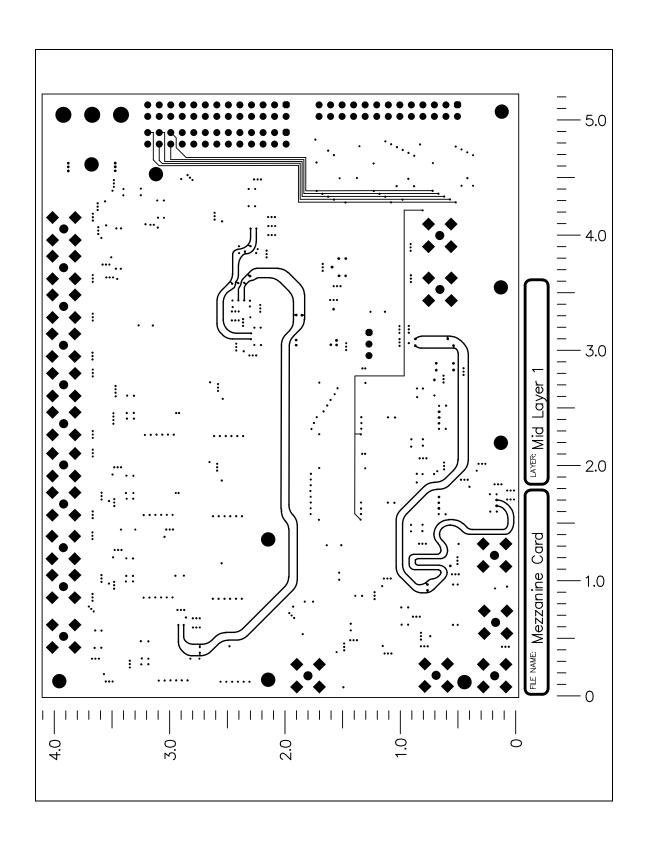

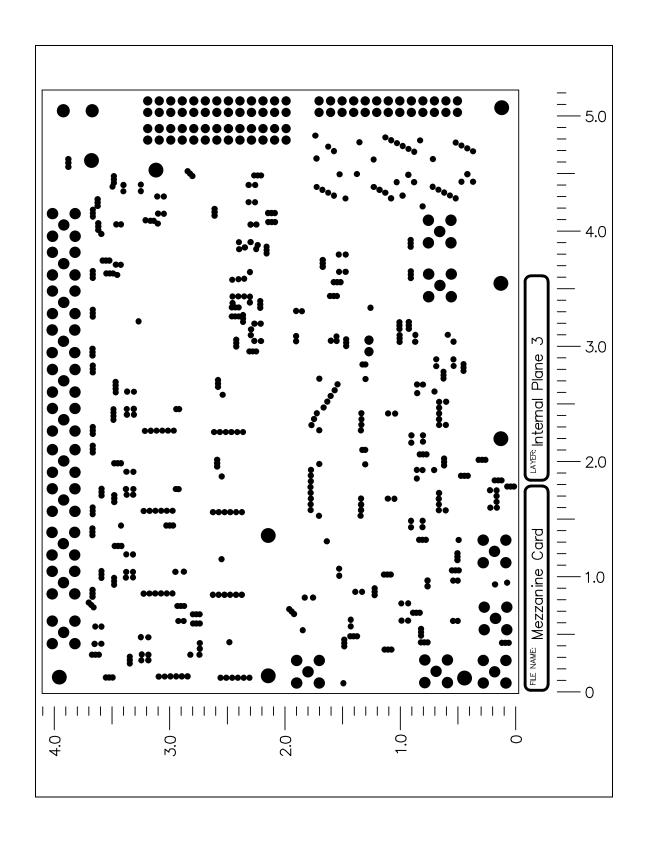

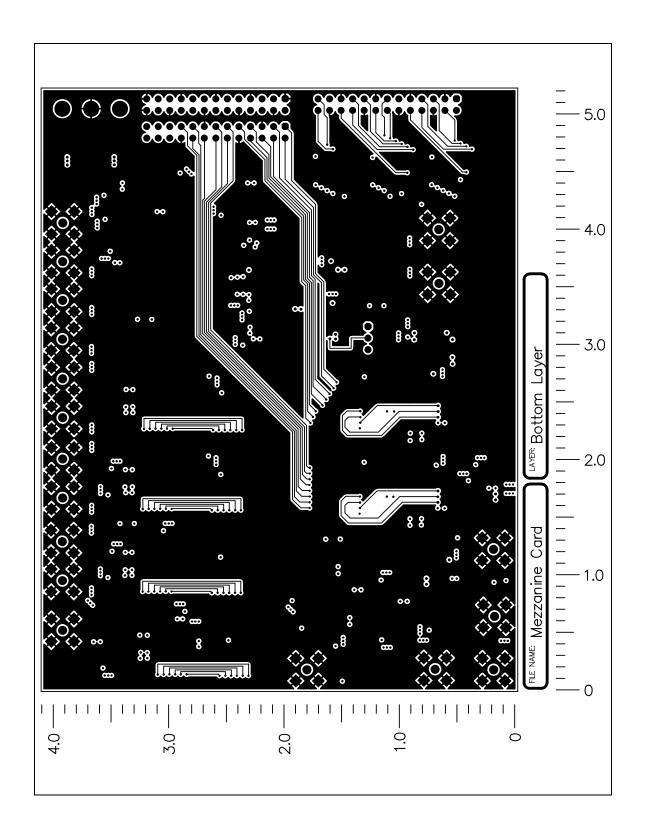

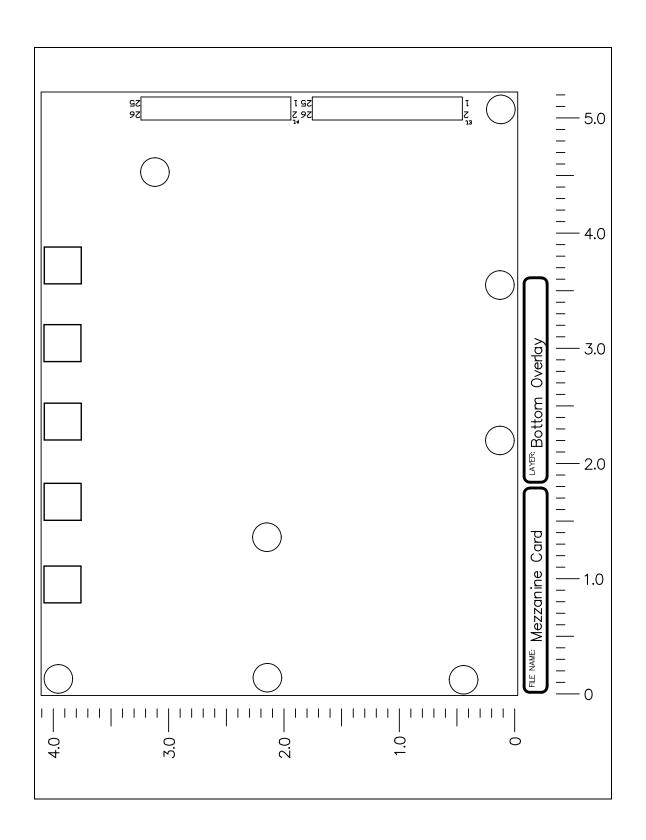

| APPEN | DIX I    | TIMING MEZZANINE CARD PCB LAYOUT | 270 |

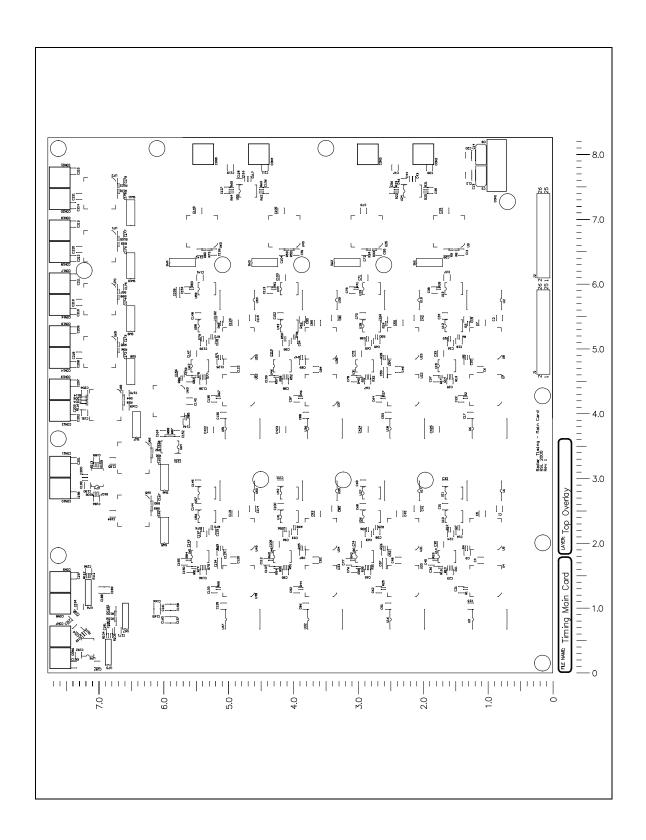

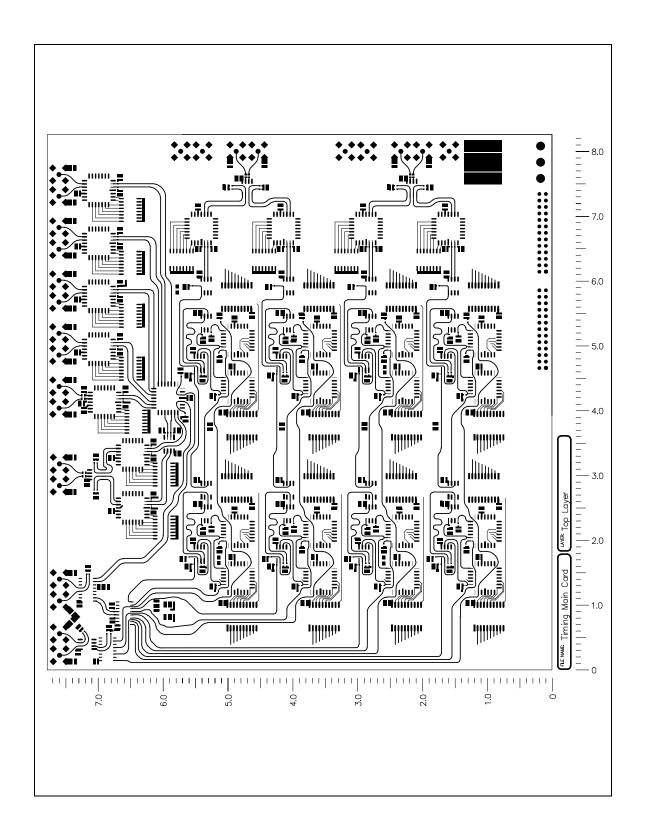

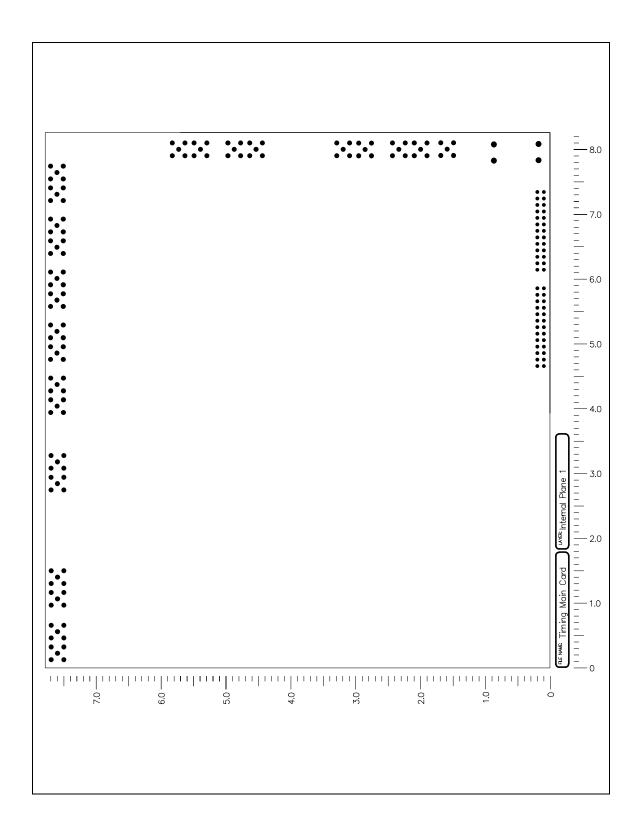

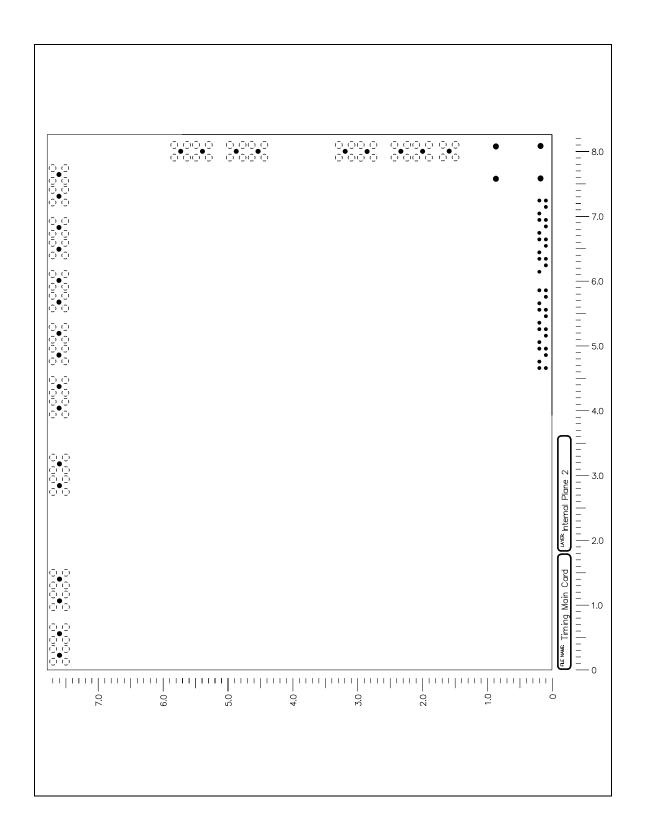

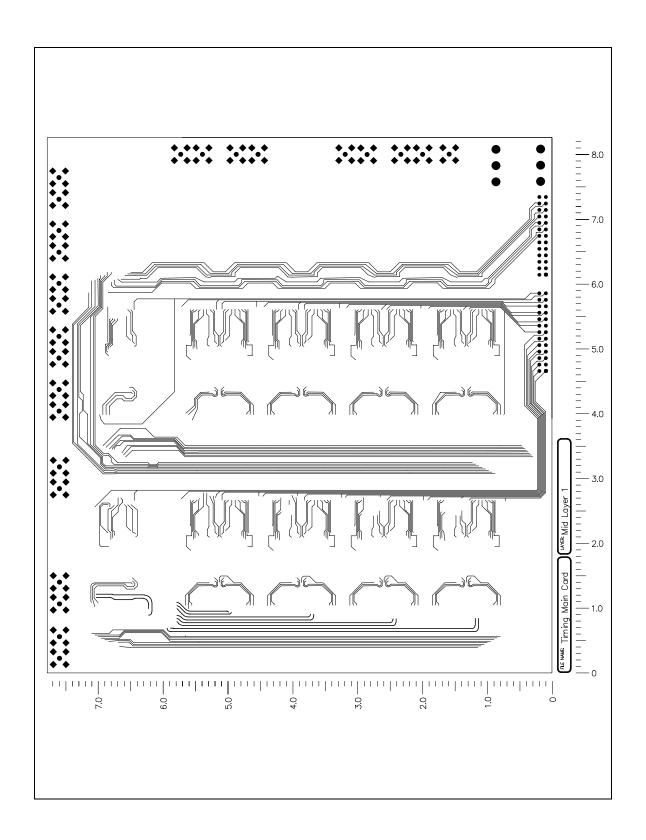

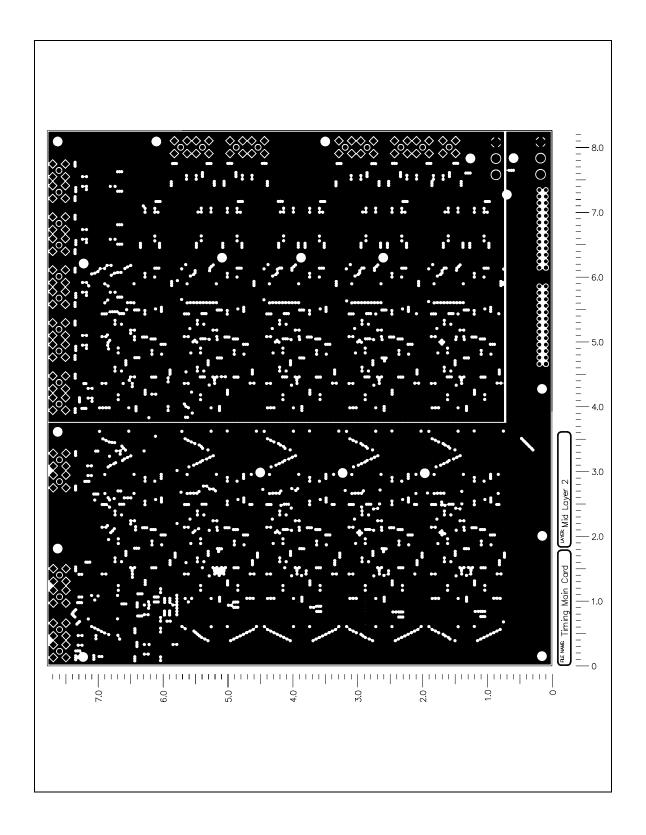

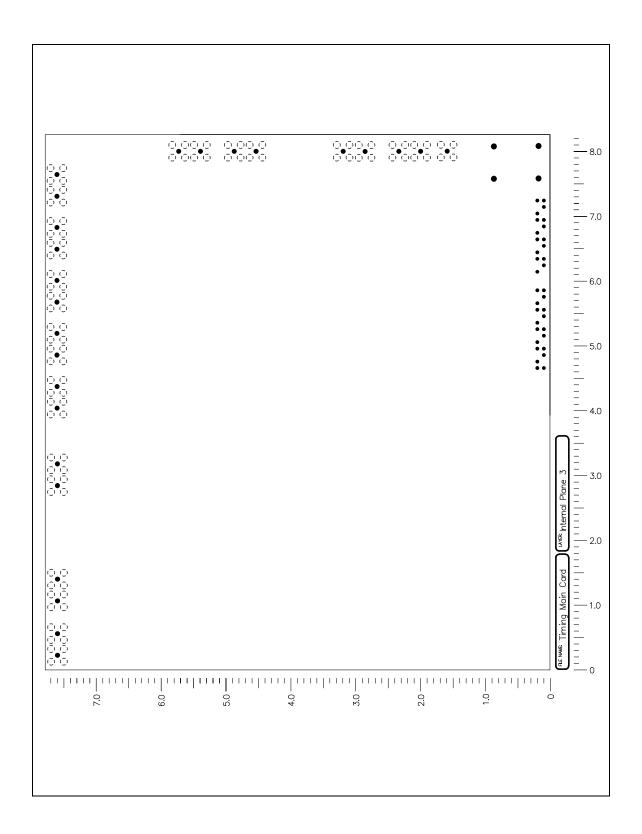

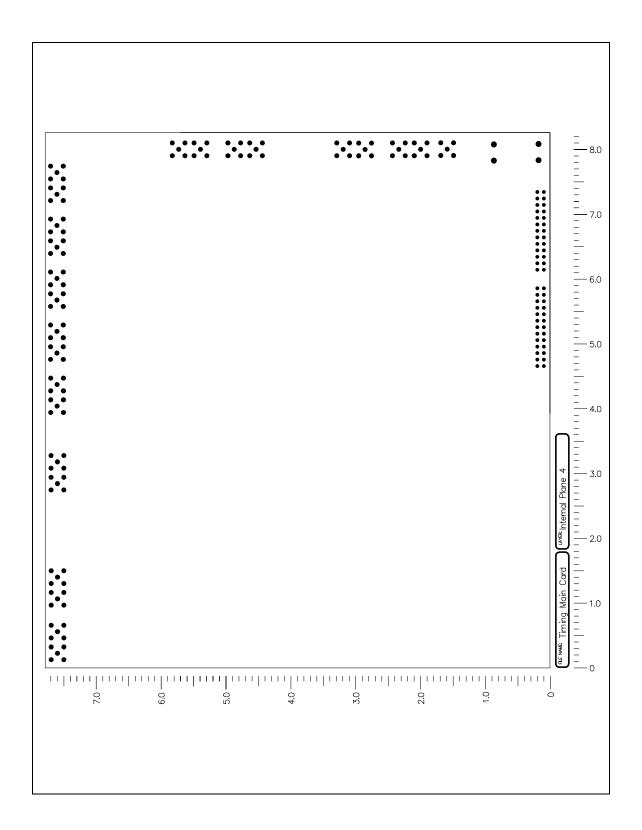

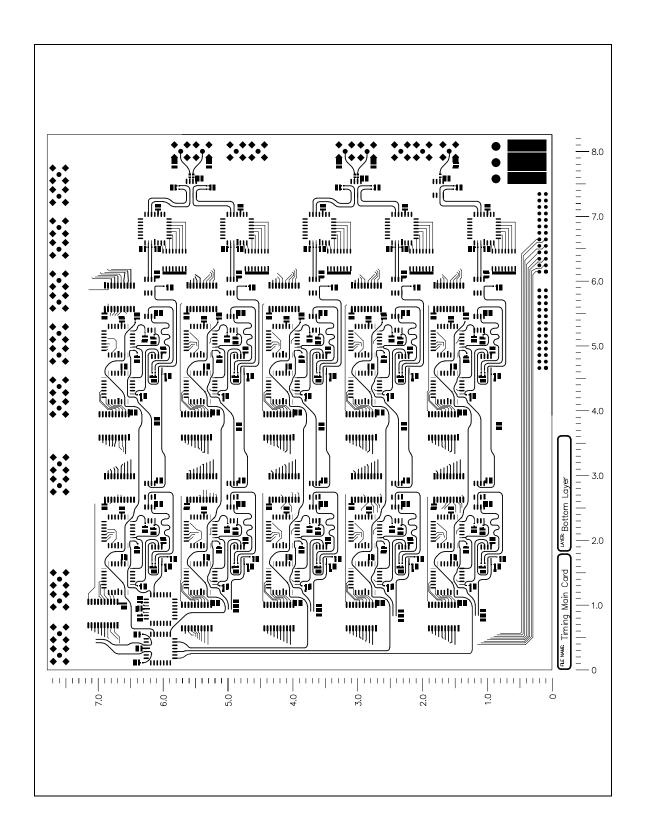

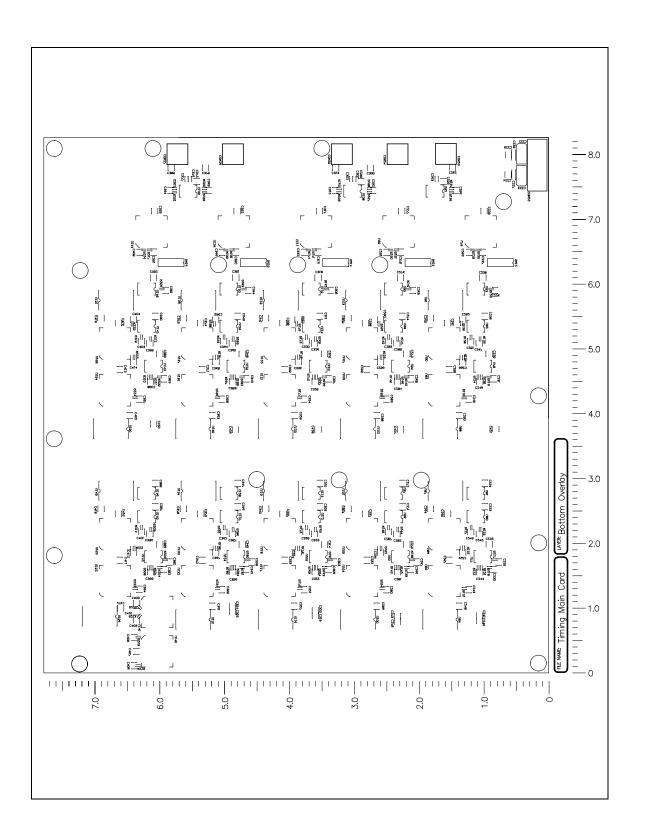

| APPEN | DIX J    | TIMING MAIN CARD PCB LAYOUT      | 279 |

| APPEN | DIX K    | PLD PROGRAMS                     | 290 |

| APPEN | DIX L    | AVERAGING CARD DSP CODE          | 300 |

| APPEN | DIX M    |                                  |     |

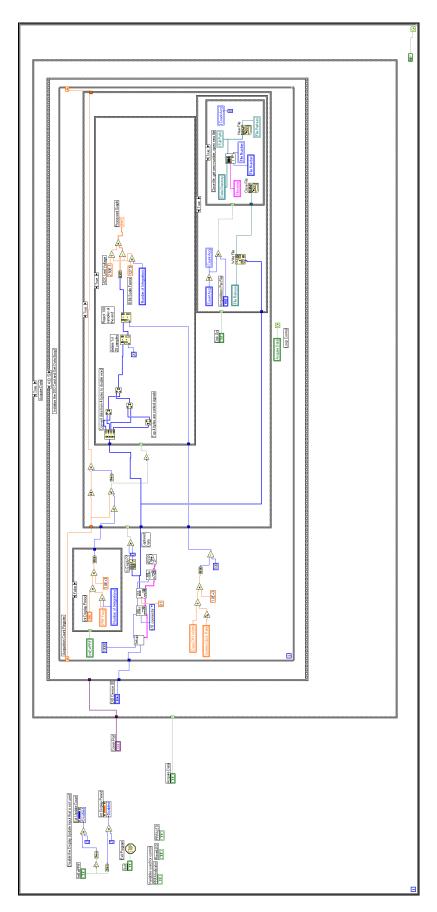

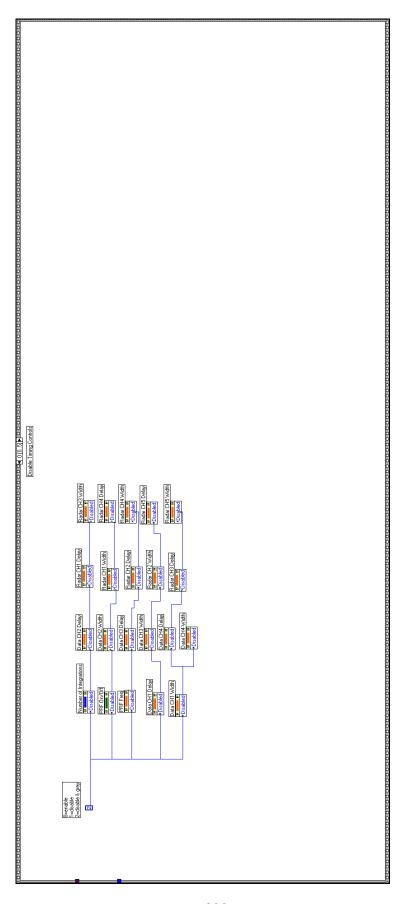

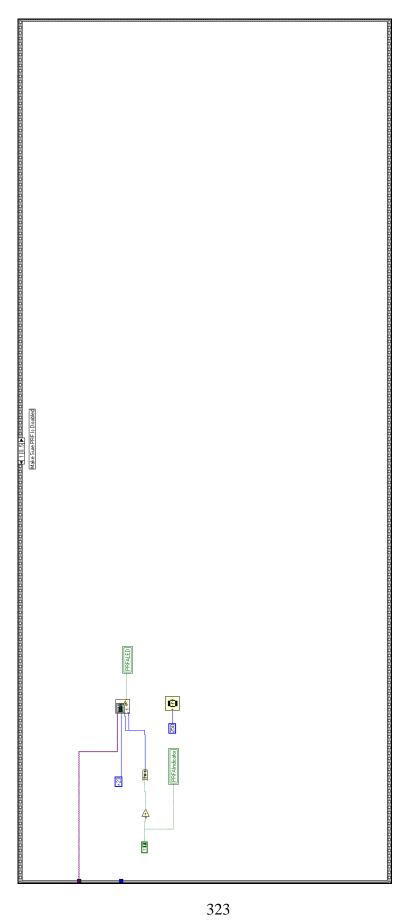

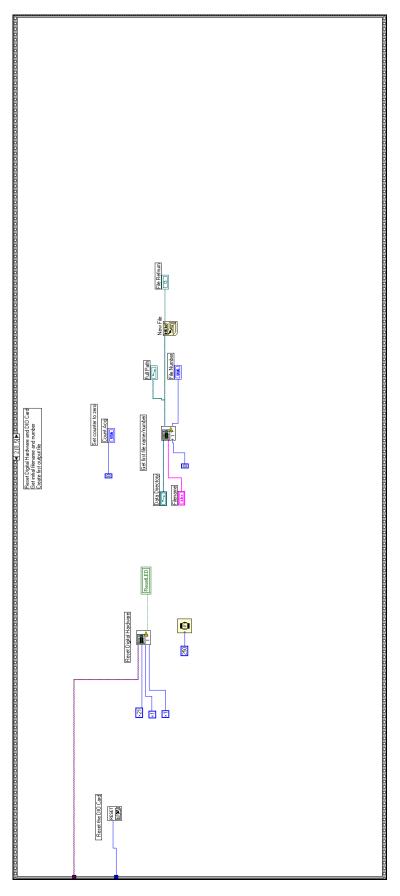

| APPEN | DIX N    | LABVIEW DATA ACQUISITION PROGRAM | 319 |

## **List of Figures**

| Figure 2-1 Frequency Domain of Traditional Sampling                                |           |

|------------------------------------------------------------------------------------|-----------|

| Figure 2-2 Aliasing Example (Frequency Domain)                                     | 5         |

| Figure 2-3 Aliasing Example (Time Domain)                                          | 5         |

| Figure 2-4 Undersampling from Even and Odd Nyquist Zones                           | 6         |

| Figure 2-5 Time Domain Example of Two Converter Interleaving                       | 10        |

| Figure 2-6 Spurious Components due to Mismatched Interleaving                      | 11        |

| Figure 2-7 Coherent Sampling of Repetitive (Radar) Signals                         | 13        |

| Figure 3-1 Overview of the Data Acquisition System                                 |           |

| Figure 3-2 A/D Convertor Card Overview                                             |           |

| Figure 3-3 Tangential Loss vs Frequency for a One Inch Trace                       | 18        |

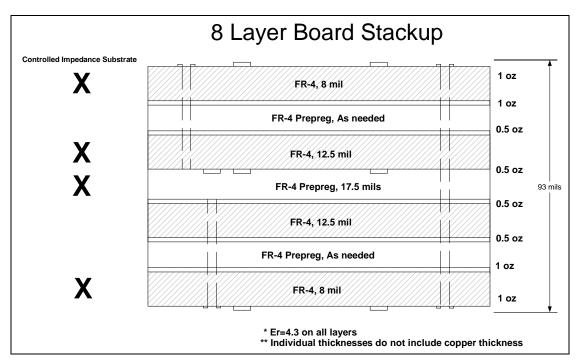

| Figure 3-4 ADC Circuit Board Stackup                                               | 19        |

| Figure 3-5 Microstrip Structures Used on High Speed Lines                          | 20        |

| Figure 3-6 Schematic Layout of the MAX104 ADC                                      | 21        |

| Figure 3-7 MAX104 Timing Diagram (Demux in Phase with Sync) [5]                    |           |

| Figure 3-8 MAX104 Timing Diagram (Demux out of Phase with Sync) [5]                |           |

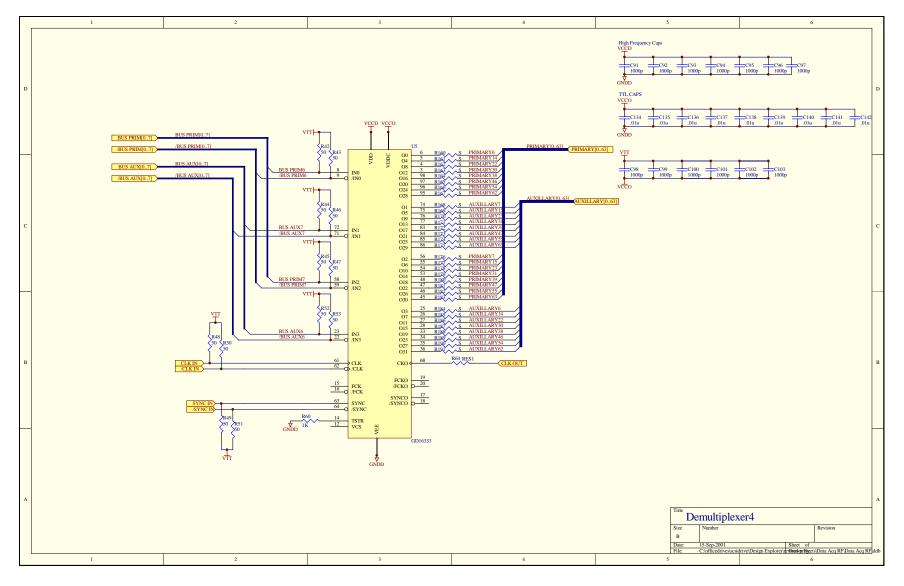

| Figure 3-9 GD16333 Demultiplexer Schematics                                        |           |

| Figure 3-10 Timing Diagram of the ADC Board                                        |           |

| Figure 3-11 Photograph of a Completed ADC Card                                     |           |

| Figure 3-12 Averaging Card Overview                                                |           |

| Figure 3-13 Averaging Card High Level Timing                                       |           |

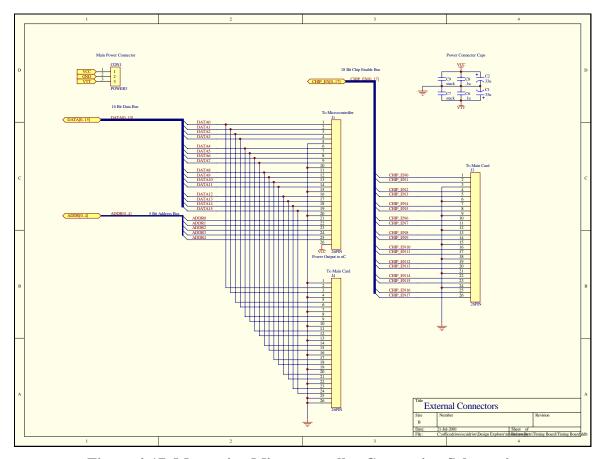

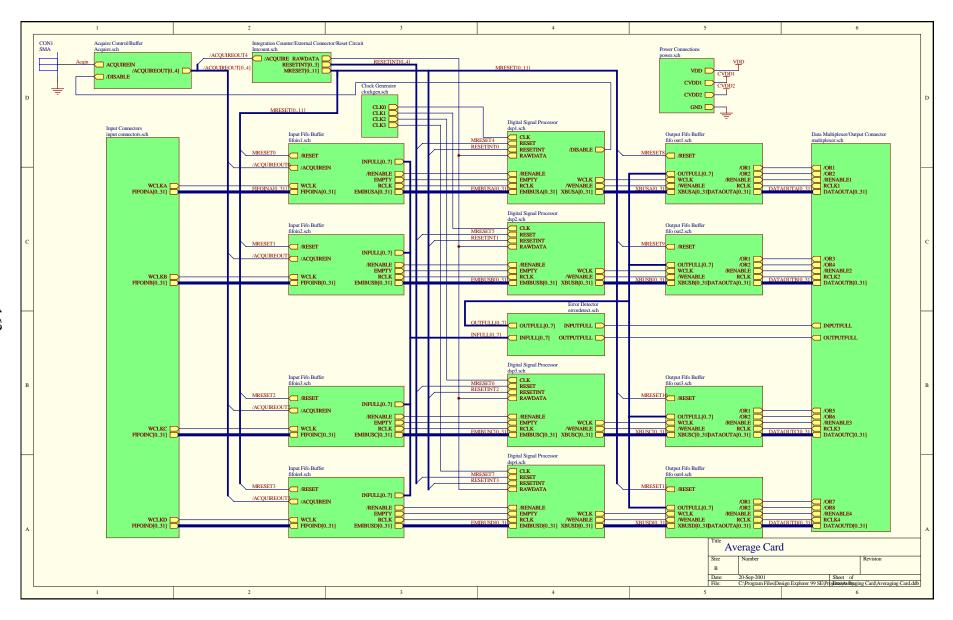

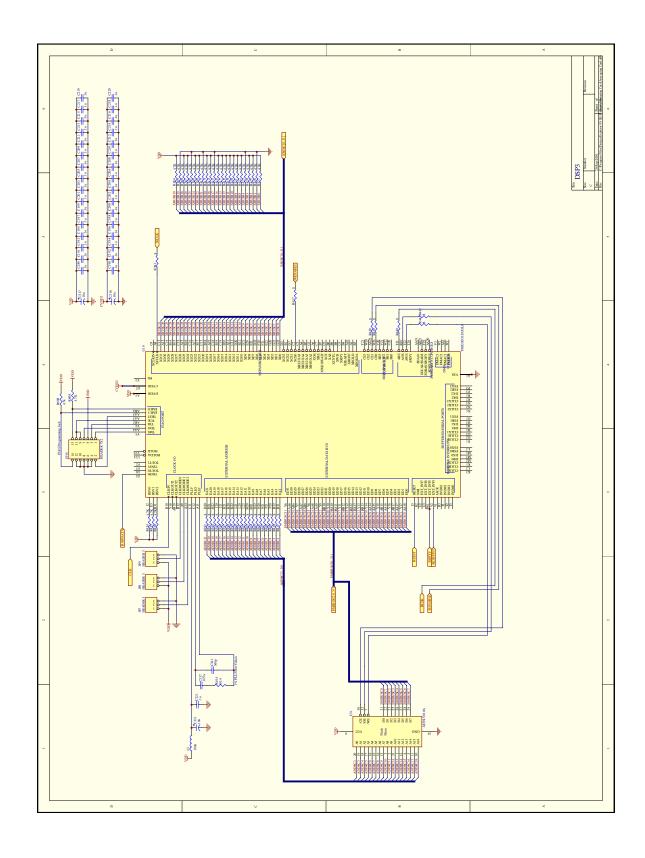

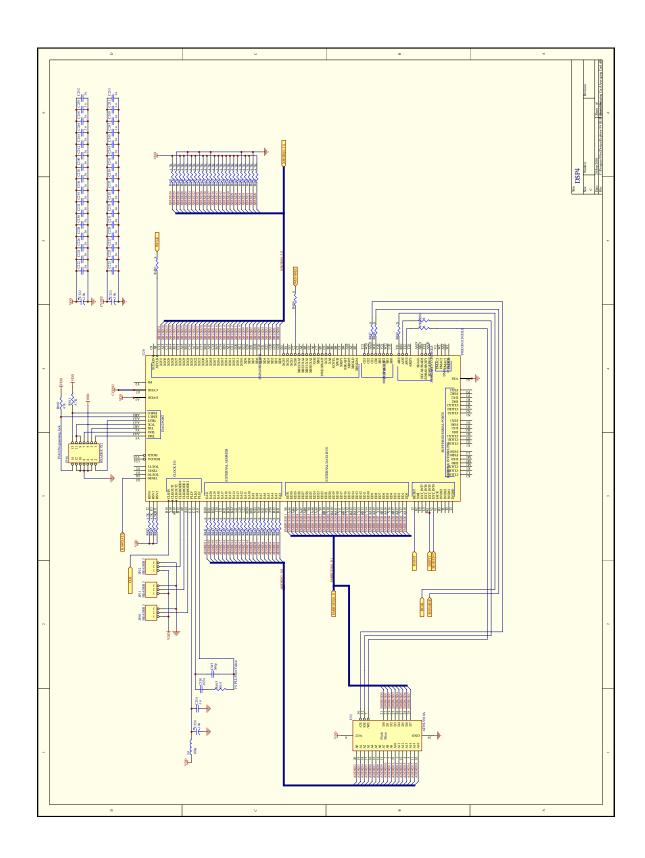

| Figure 3-14 Top level Schematic of the Averaging Card                              |           |

| Figure 3-15 Input Connector and Pinout Pattern                                     |           |

| Figure 3-16 Acquire Control Timing Diagram                                         |           |

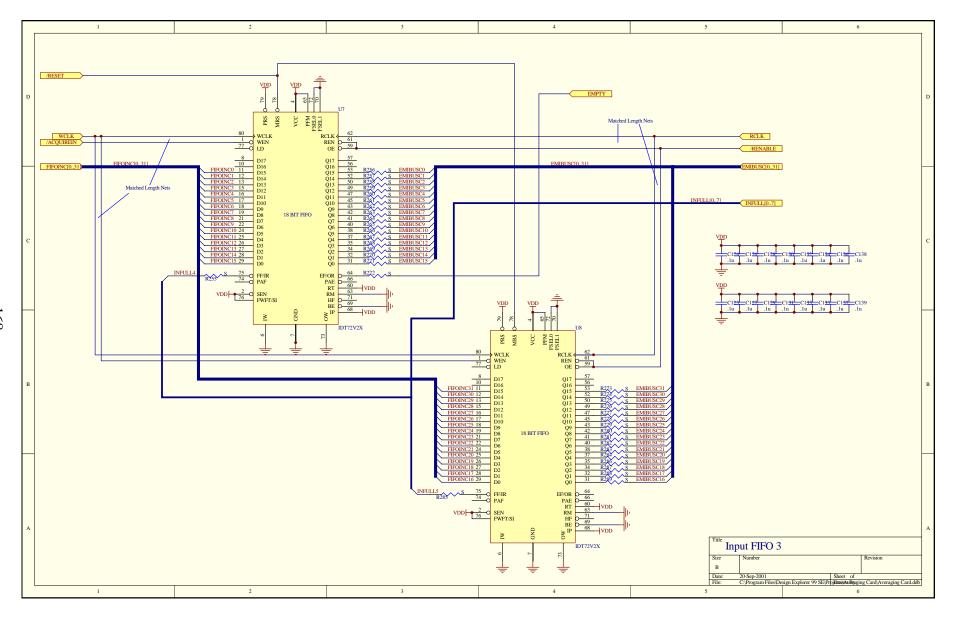

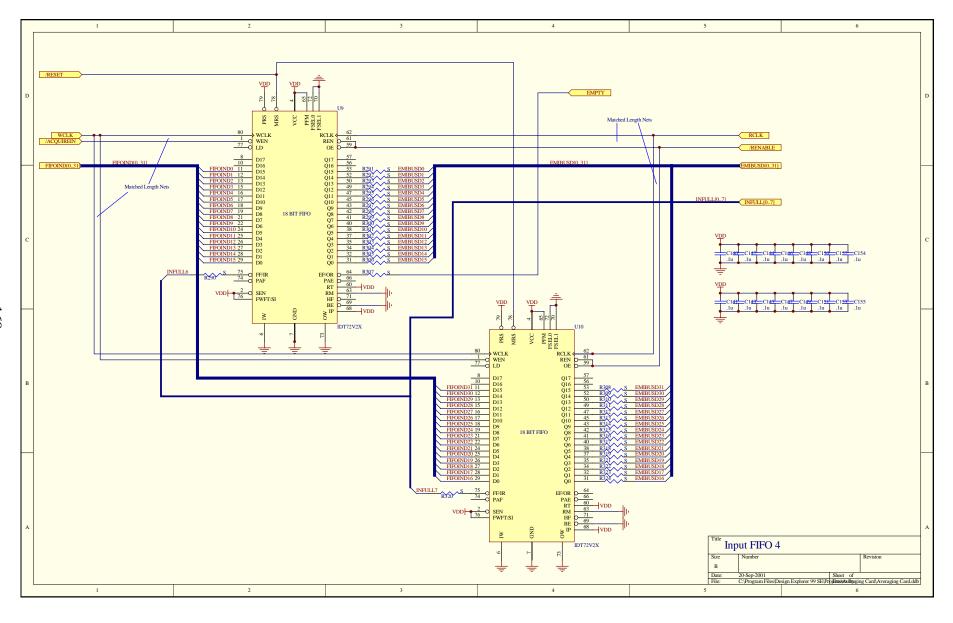

| Figure 3-17 Input FIFO Schematic                                                   |           |

| Figure 3-18 Split Transmission Line Structure for Dual FIFOs                       |           |

| Figure 3-19 Simulation Model of Input Transmission Line Structure                  |           |

| Figure 3-20 Input Transmission Line Simulation Results                             |           |

| Figure 3-21 Eye Measurement at the FIFO Inputs                                     |           |

| Figure 3-22 EESOF Simulation of the FIFO Input Data Lines                          | 40        |

| Figure 3-23 EESOF FIFO Input Data Simulation Results                               | 41        |

| Figure 3-24 Integration Counter and Reset Schematics                               | 42        |

| Figure 3-25 DSP Schematic                                                          |           |

| Figure 3-26 Flash Programming Algorithm [11]                                       | 49        |

| Figure 3-27 DSP Clock Generation Schematic                                         |           |

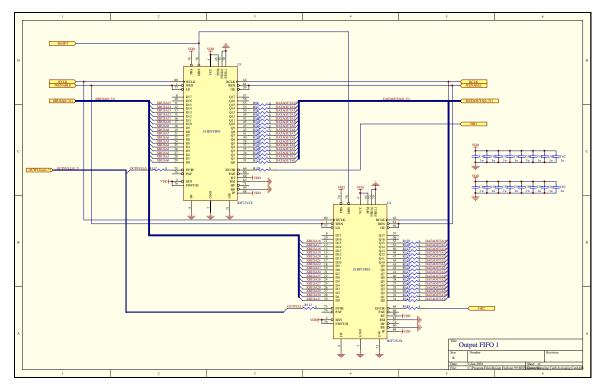

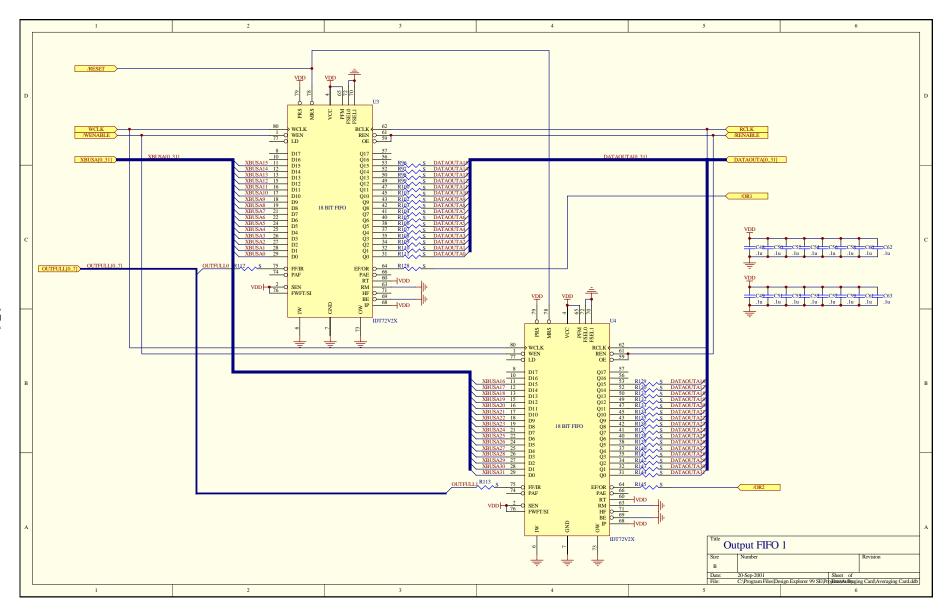

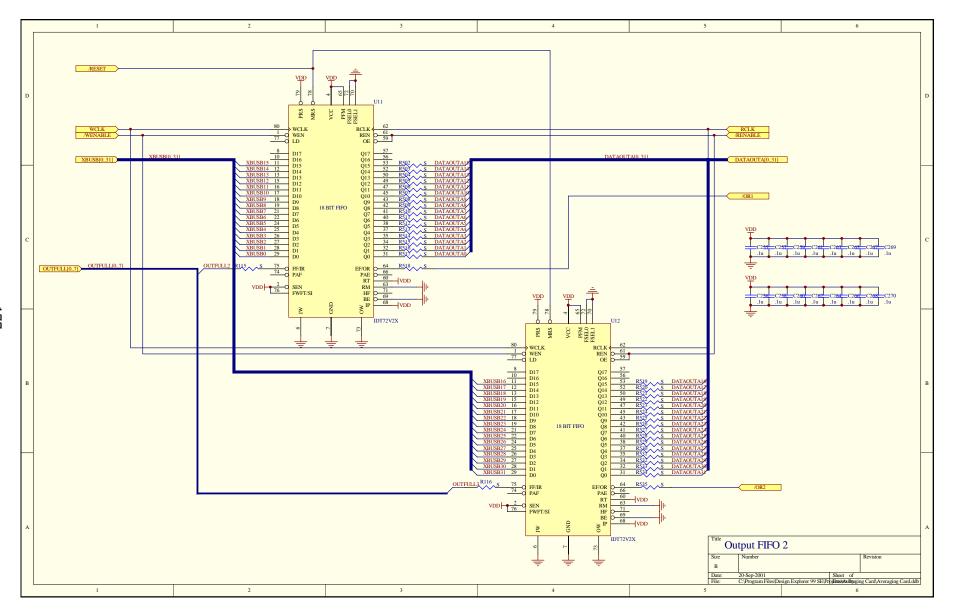

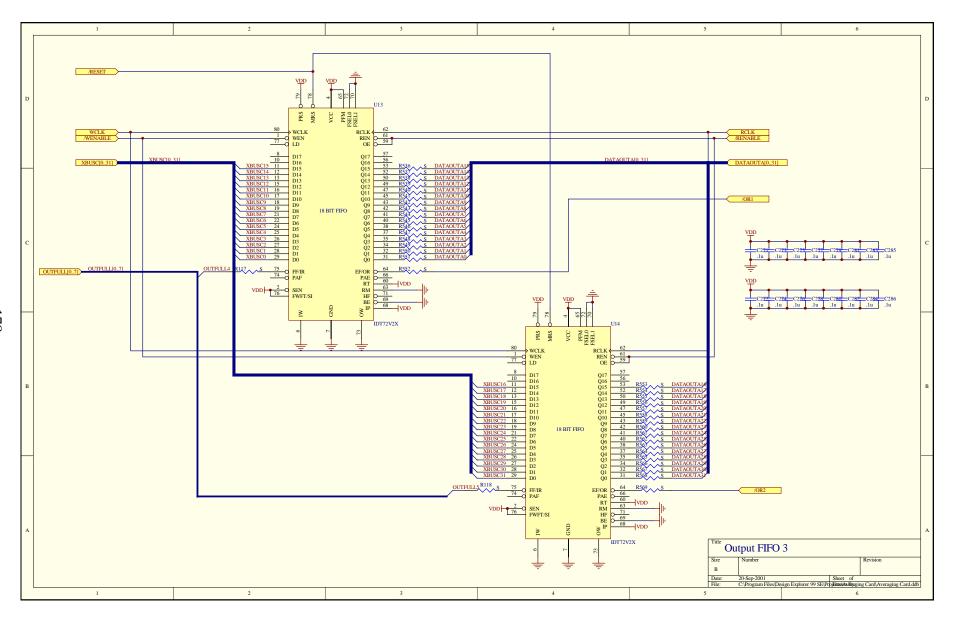

| Figure 3-28 Output FIFO Schematic                                                  |           |

| Figure 3-29 Output Multiplexer Schematic                                           |           |

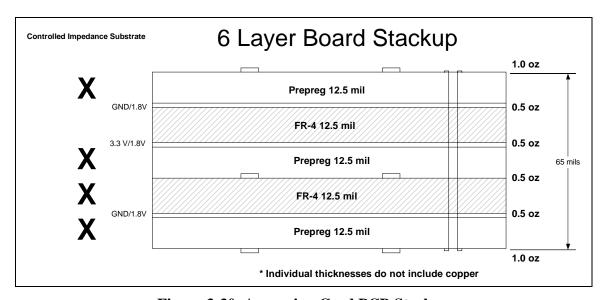

| Figure 3-30 Averaging Card PCB Stackup                                             |           |

| Figure 3-31 Averaging Card Photograph                                              |           |

| Figure 3-32 Flow Diagram of the DSP Assembly Program                               |           |

| Figure 3-33 Performance Analysis of the Integration Code                           |           |

| Figure 3-34 Overview of Flash Programming and Boot Loading                         |           |

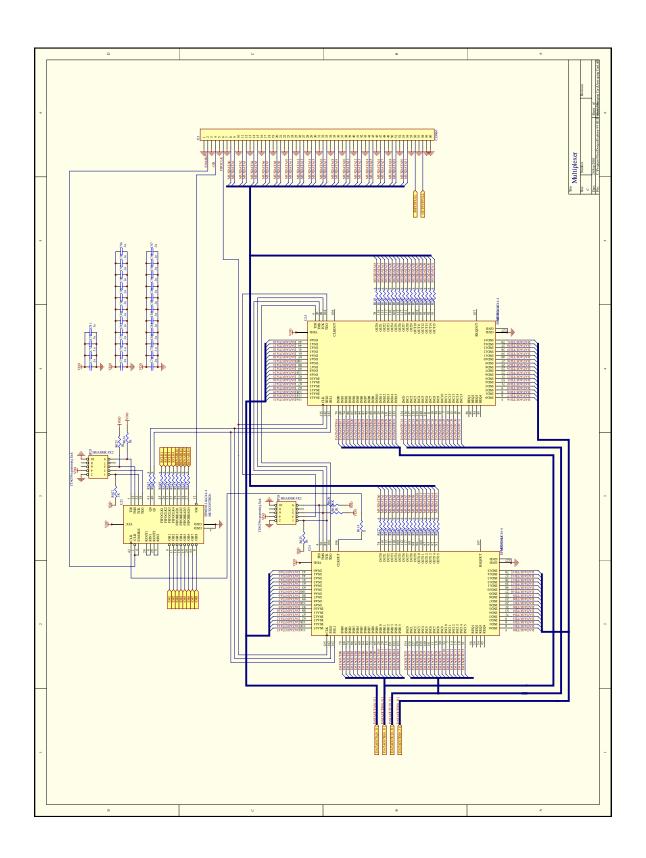

| Figure 3-35 Multiplexer Card Overview                                              |           |

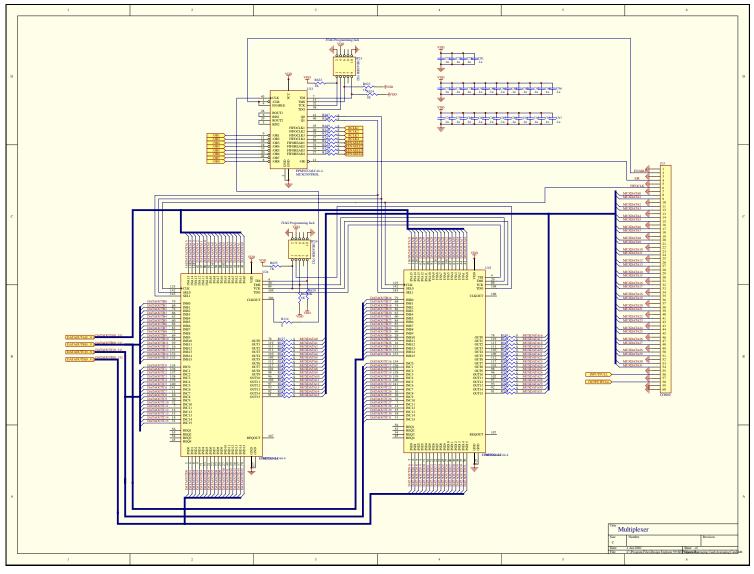

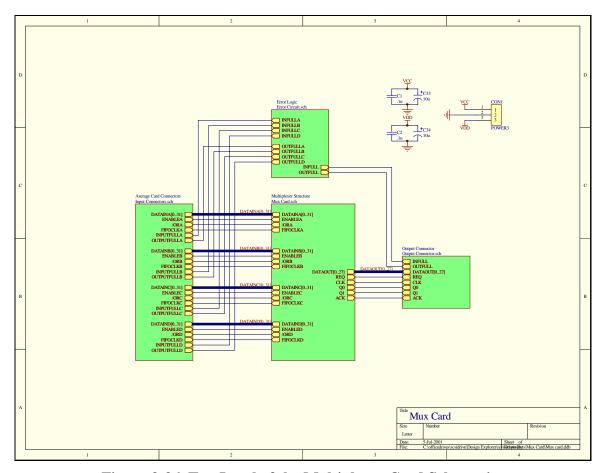

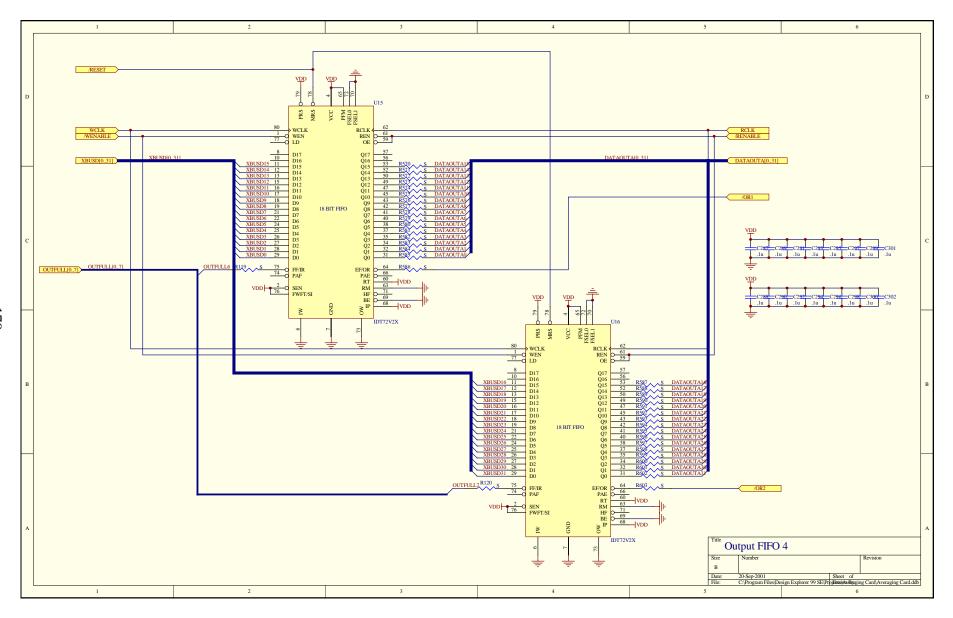

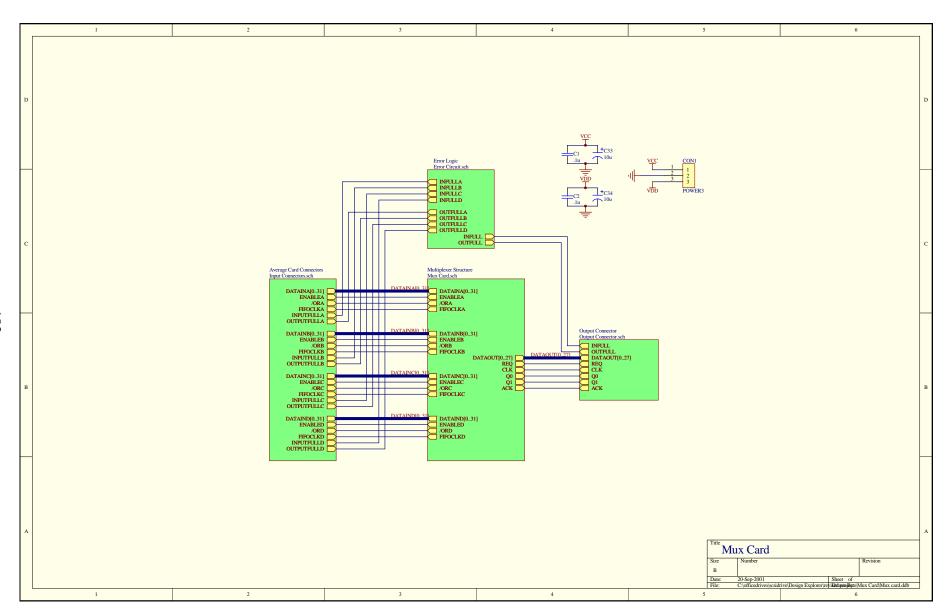

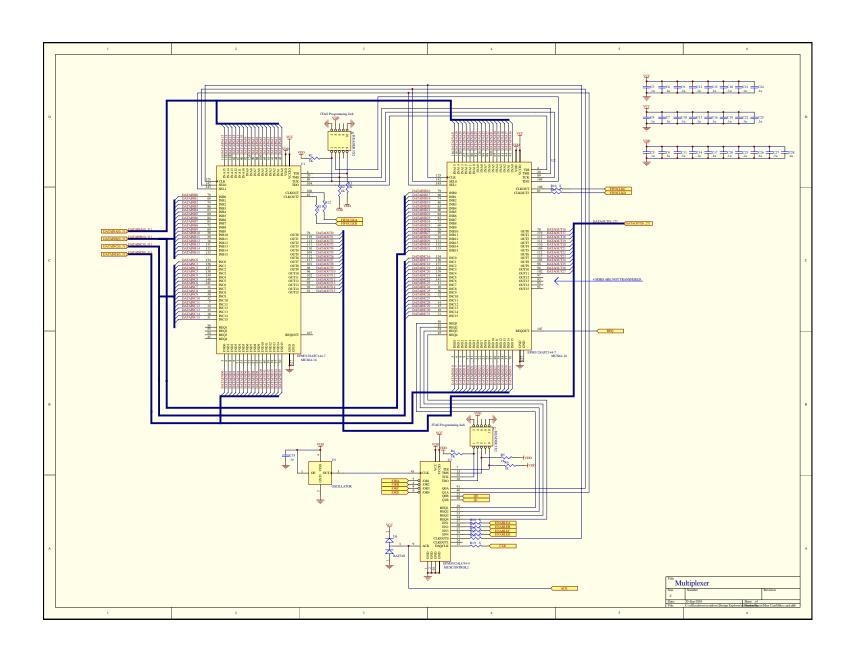

| Figure 3-36 Top Level of the Multiplexer Card Schematics                           |           |

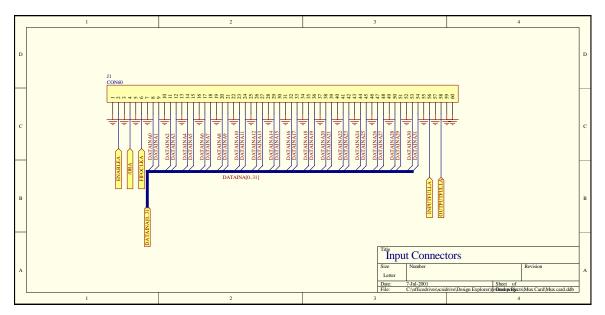

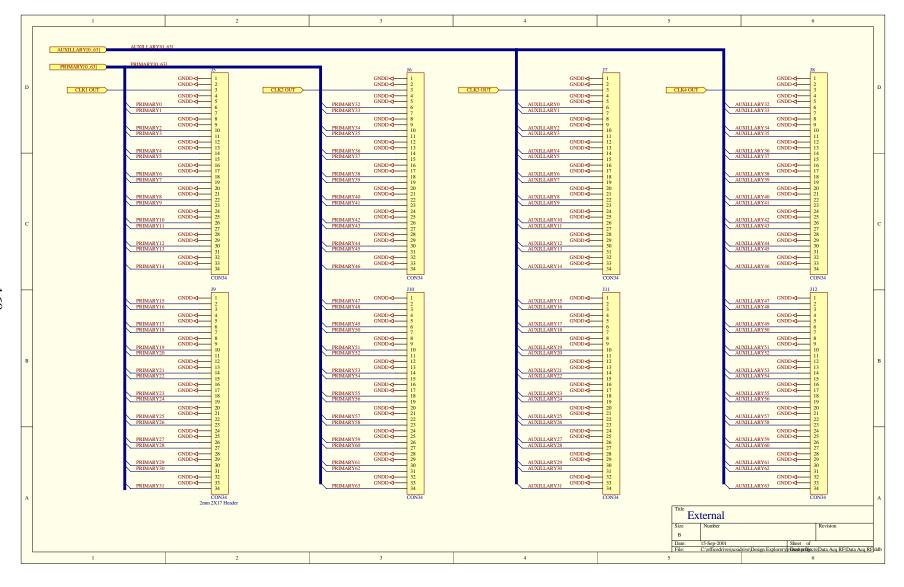

| Figure 3-37 Mux Card Input Connector Pinout                                        |           |

| Figure 3-38 Multiplexer Schematic                                                  |           |

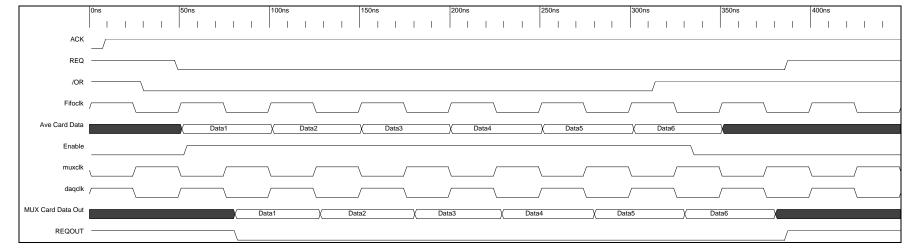

| Figure 3-39 Mux Card Timing Diagram                                                |           |

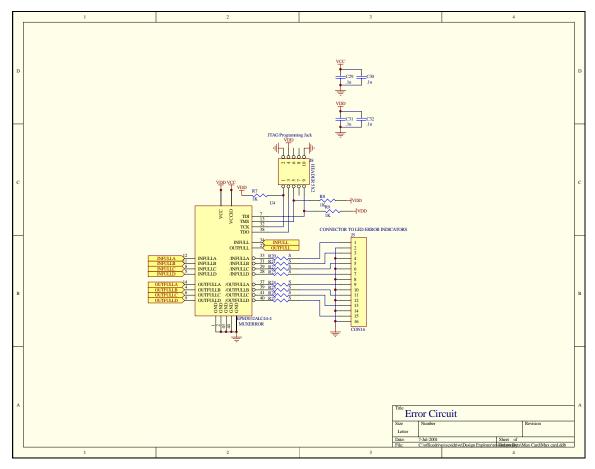

| Figure 3-40 Error Logic Schematic                                                  |           |

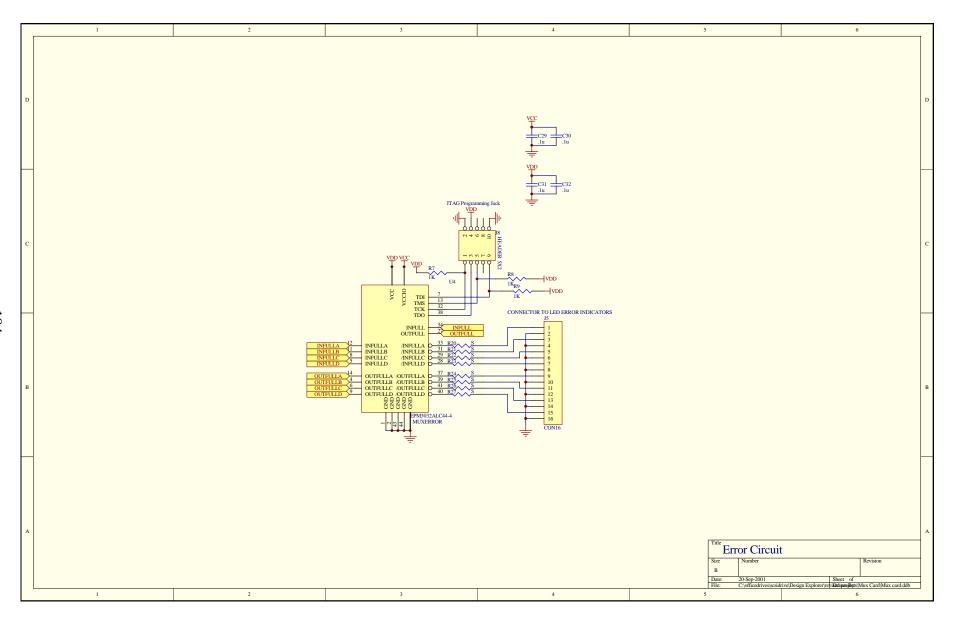

| Figure 3-40 Error Logic Schematic                                                  |           |

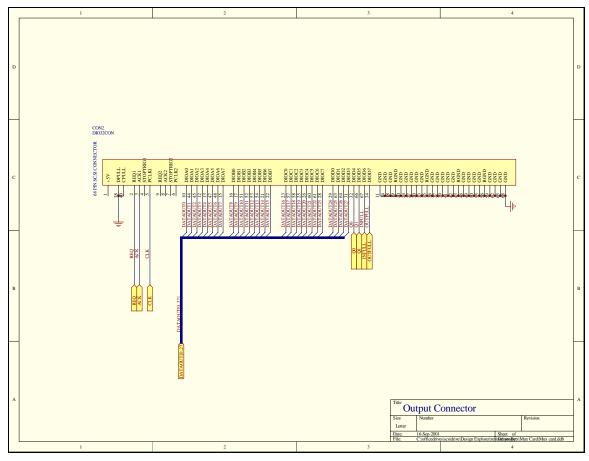

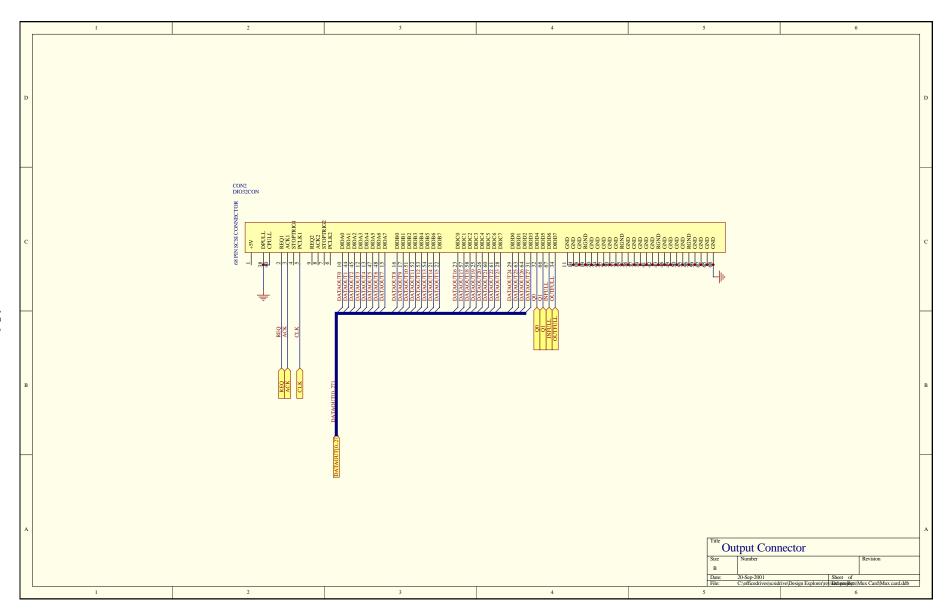

| Figure 3-41 Output Connector Schematic                                             |           |

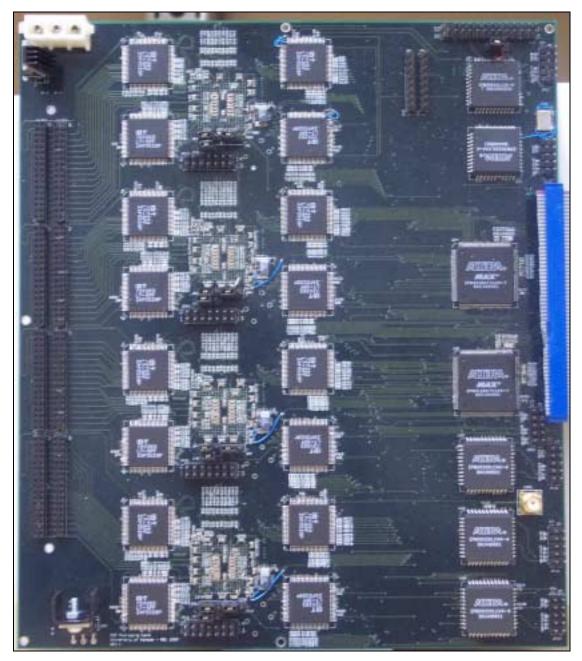

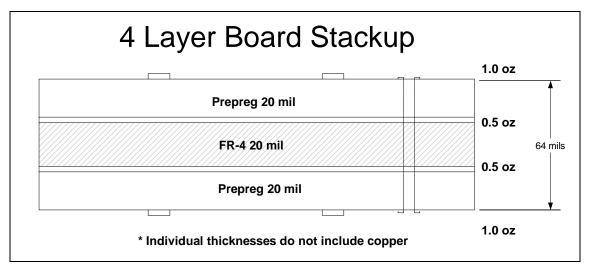

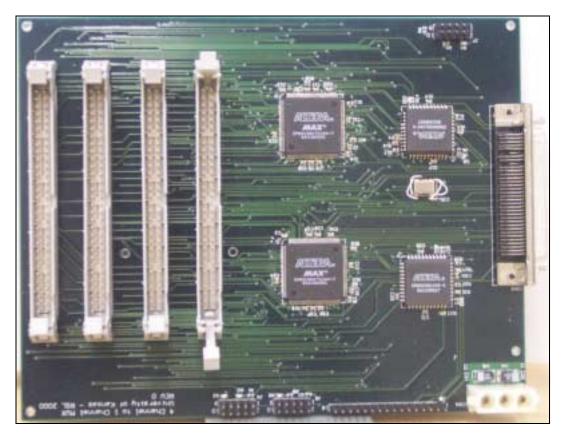

| Figure 3-42 Multiplexer PCB StackupFigure 3-43 Multiplexer Card Photograph         | / /<br>77 |

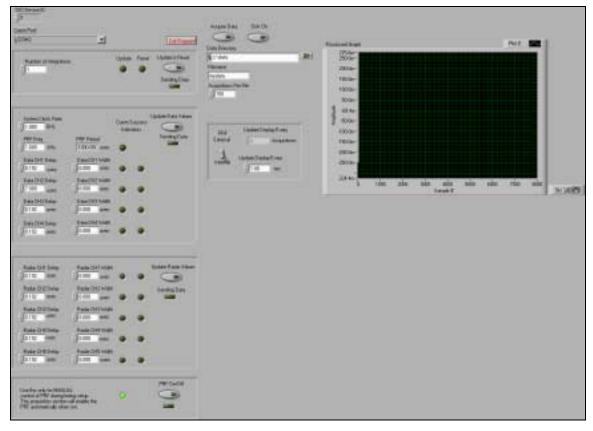

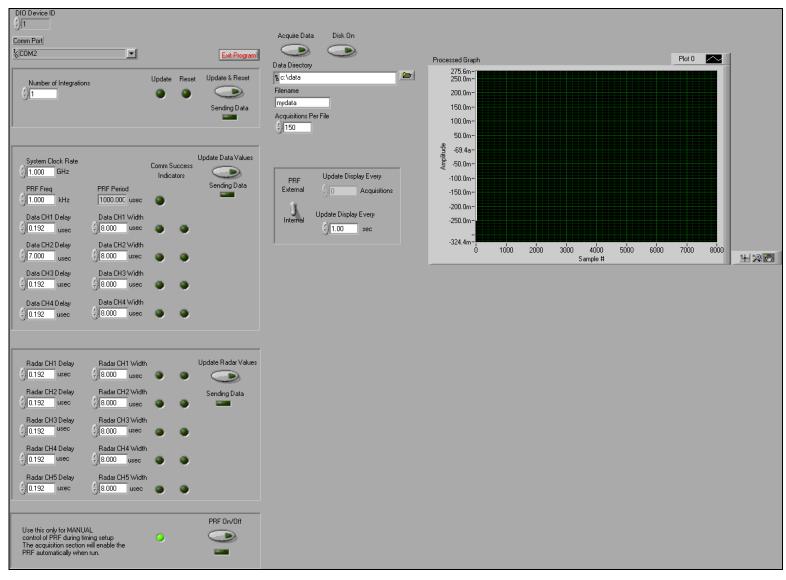

| Figure 3-43 Multiplexer Card PhotographFigure 3-44 Acquisition Software Screenshot |           |

|                                                                                    |           |

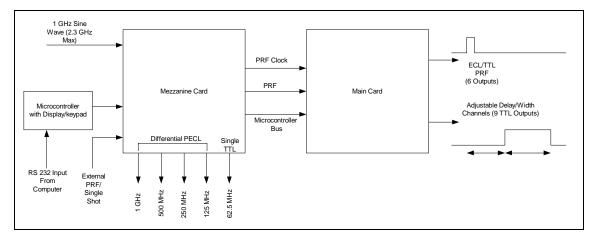

| Figure 4-1 Timing System Overview                                                  |           |

| Figure 4-2 Simplified Schematic of an ECL Gate [13]                                |           |

| Figure 4-3 Typical Biasing and Termination Methods for ECL Gates                   |           |

| Figure 4-4 ECL and PECL Supply Requirements                                        | ð/        |

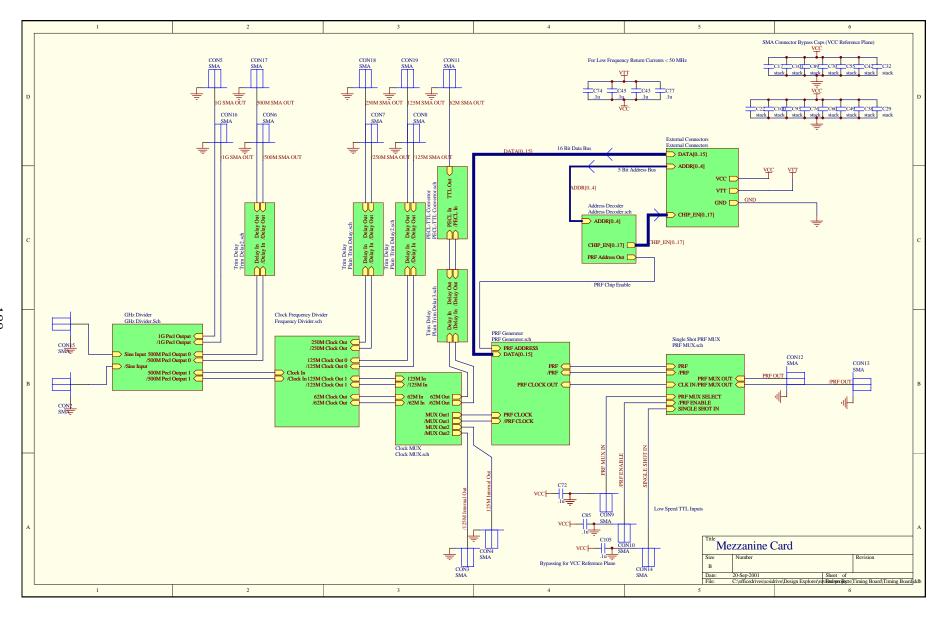

| Figure 4-5 Mezzanine Card Overview                                    |       |

|-----------------------------------------------------------------------|-------|

| Figure 4-6 Mezzanine Card Top Level Schematic                         |       |

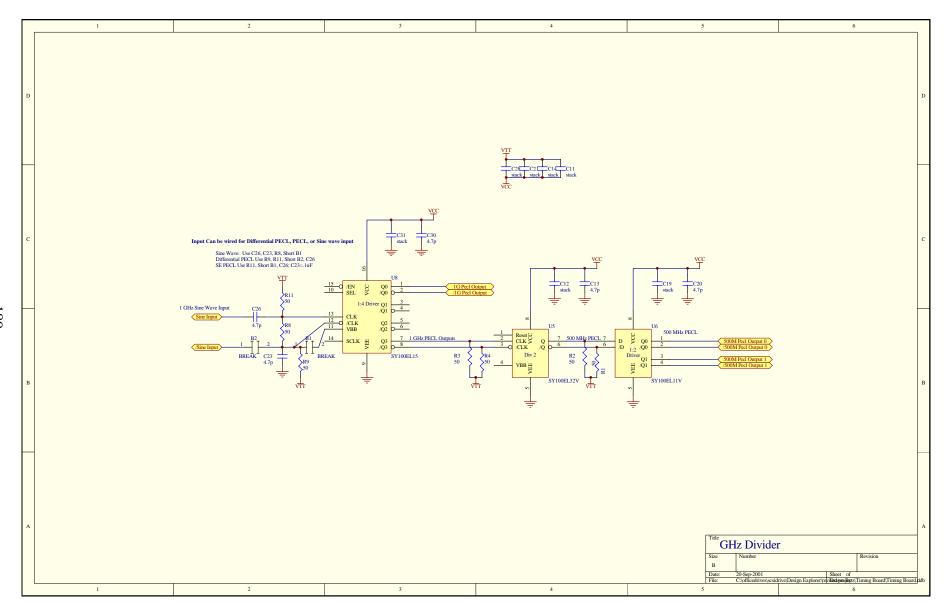

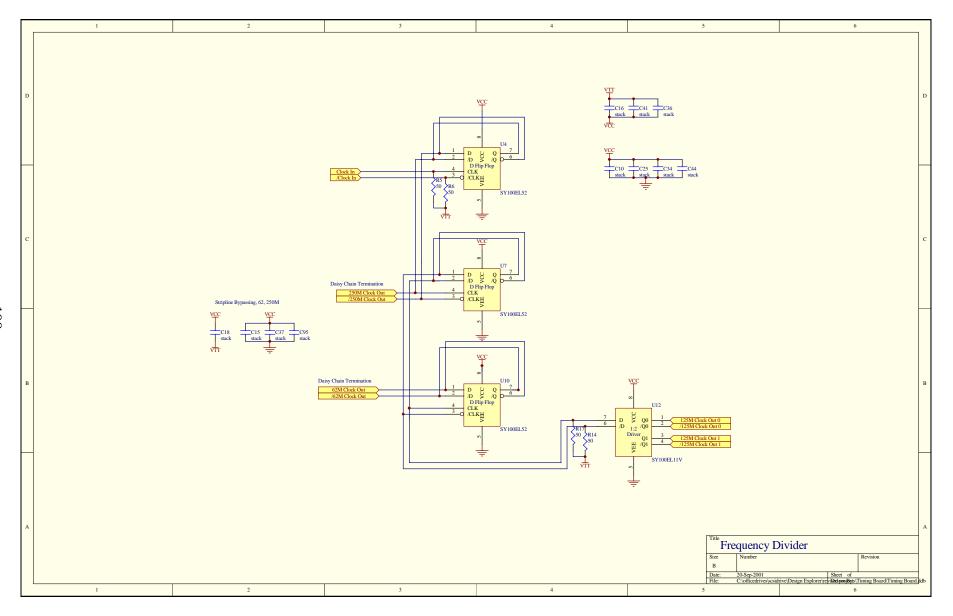

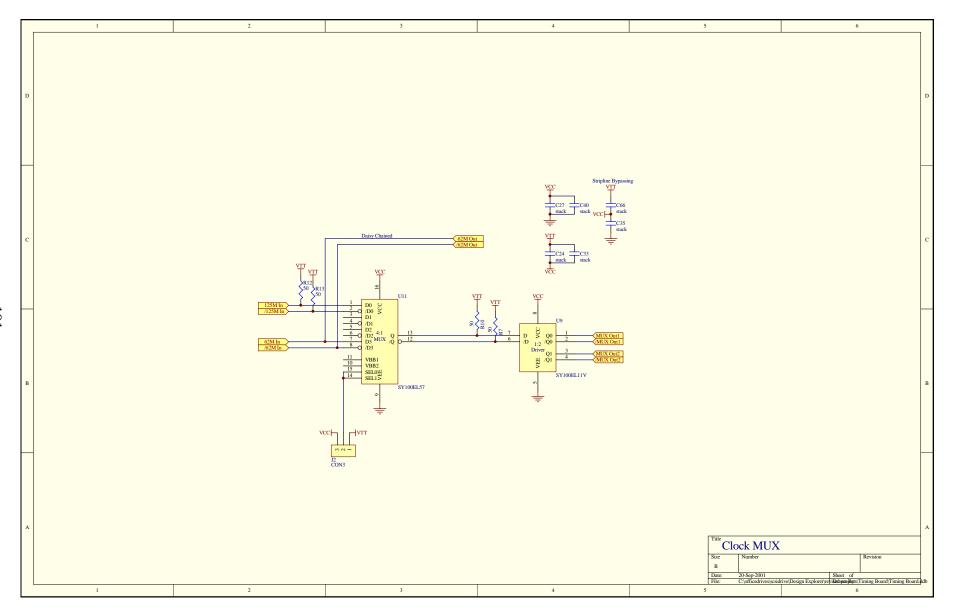

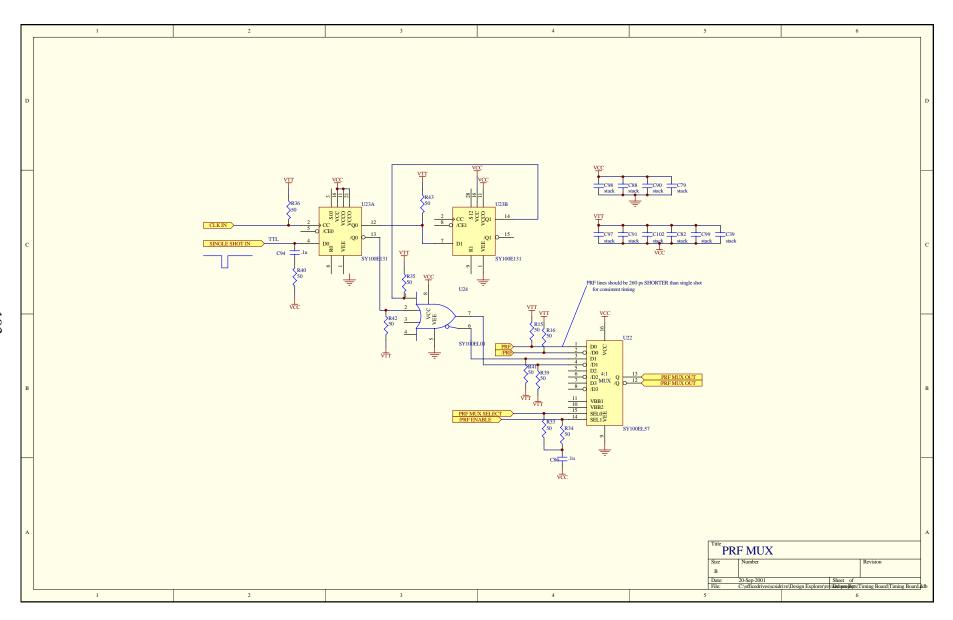

| Figure 4-7 GHz Divider Schematic                                      |       |

| Figure 4-8 Mezzanine Card Clock Input Configurations                  |       |

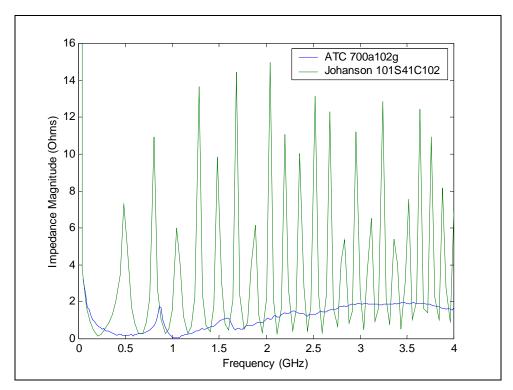

| Figure 4-9 Comparison of Standard and RF Capacitor Frequency Response | 95    |

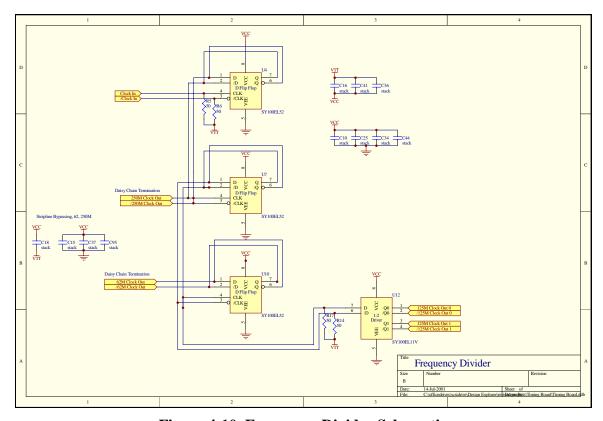

| Figure 4-10 Frequency Divider Schematic                               | 96    |

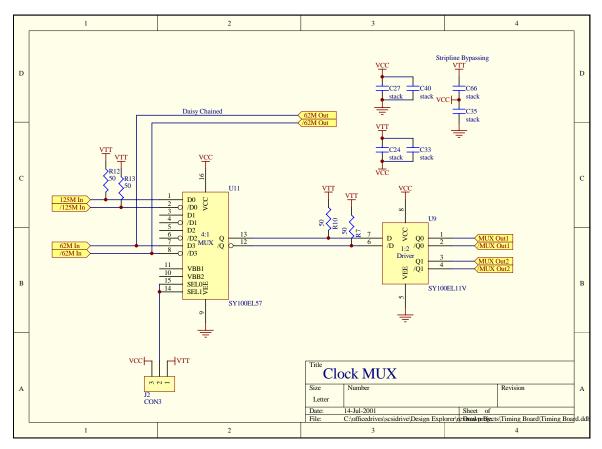

| Figure 4-11 Clock Mux Schematic                                       | 97    |

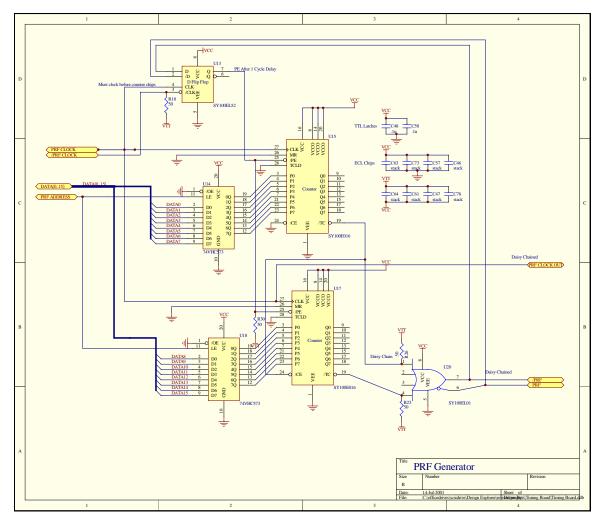

| Figure 4-12 PRF Generator Schematic                                   | 98    |

| Figure 4-13 PRF Generator Timing Diagram                              | 98    |

| Figure 4-14 PRF Mux Schematic                                         | . 101 |

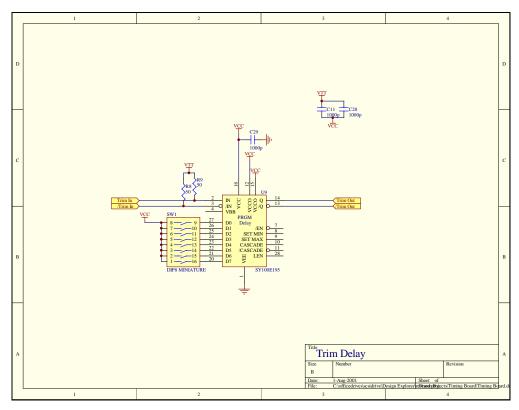

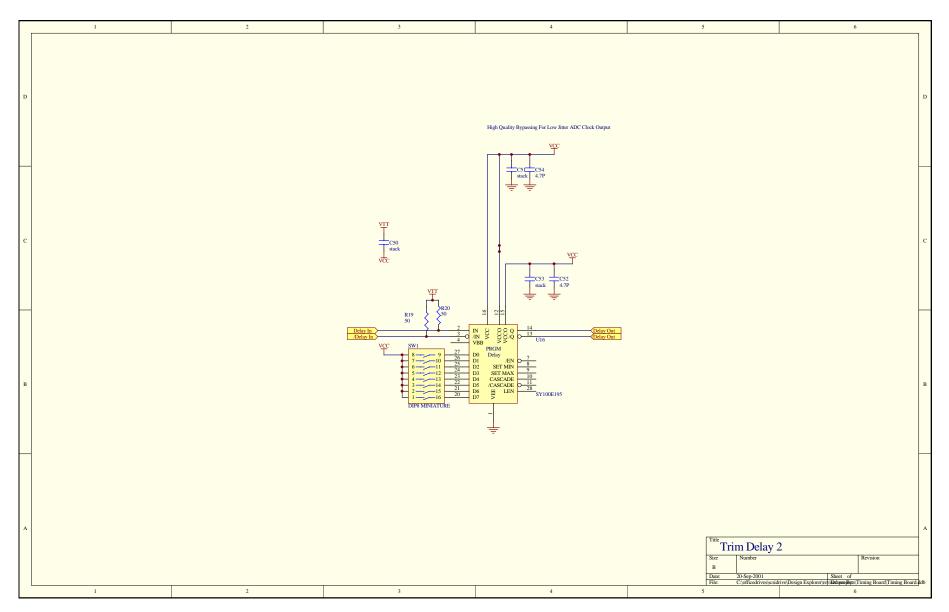

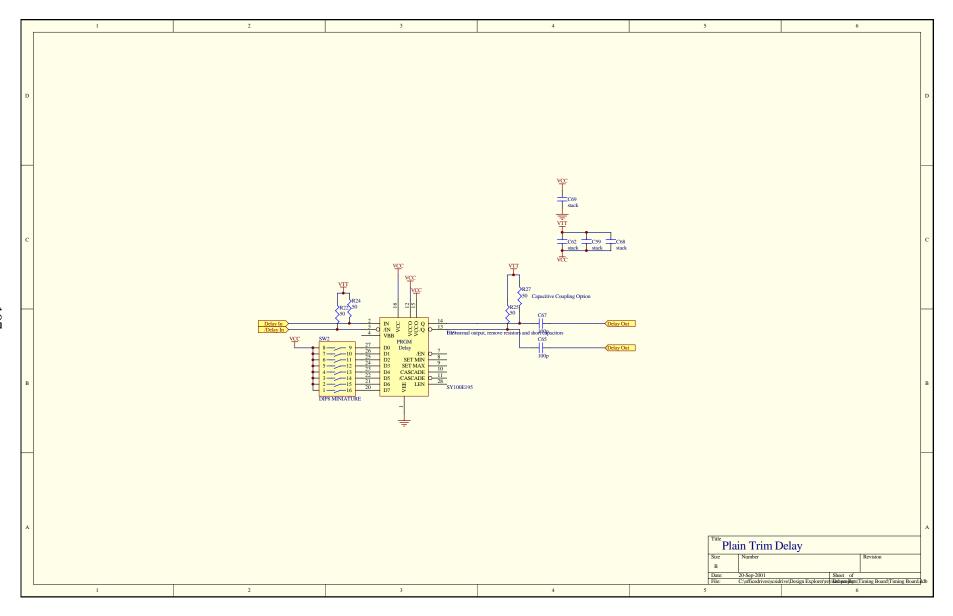

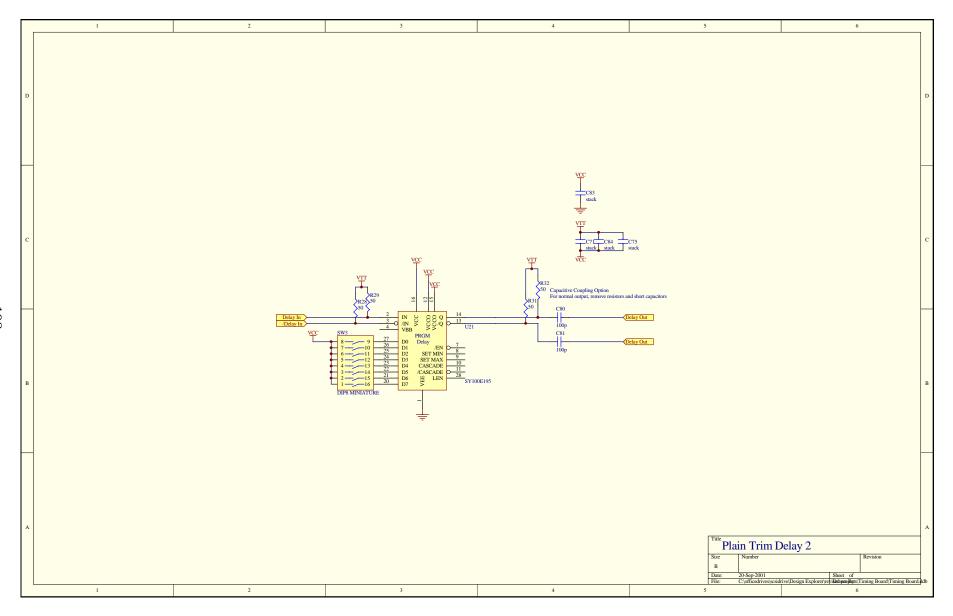

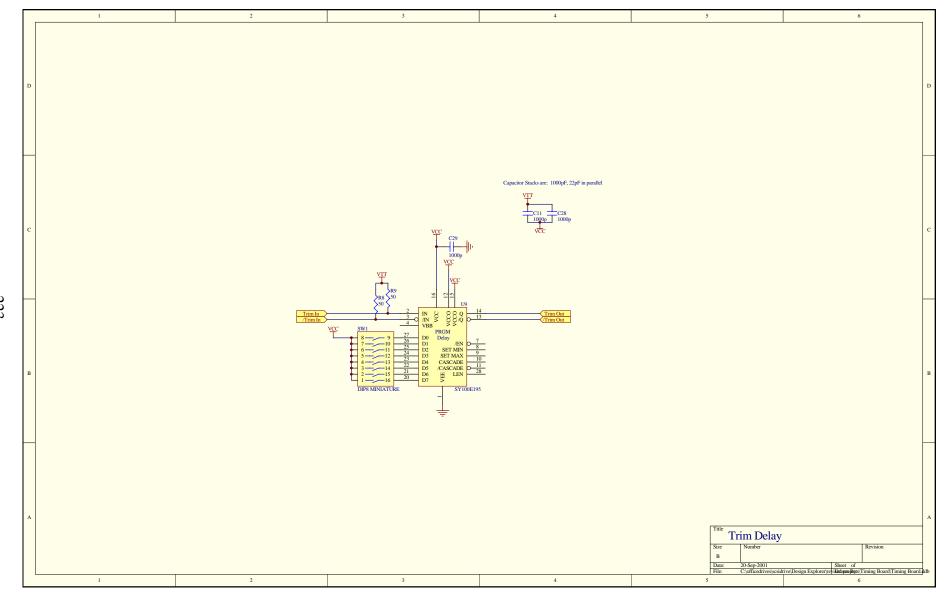

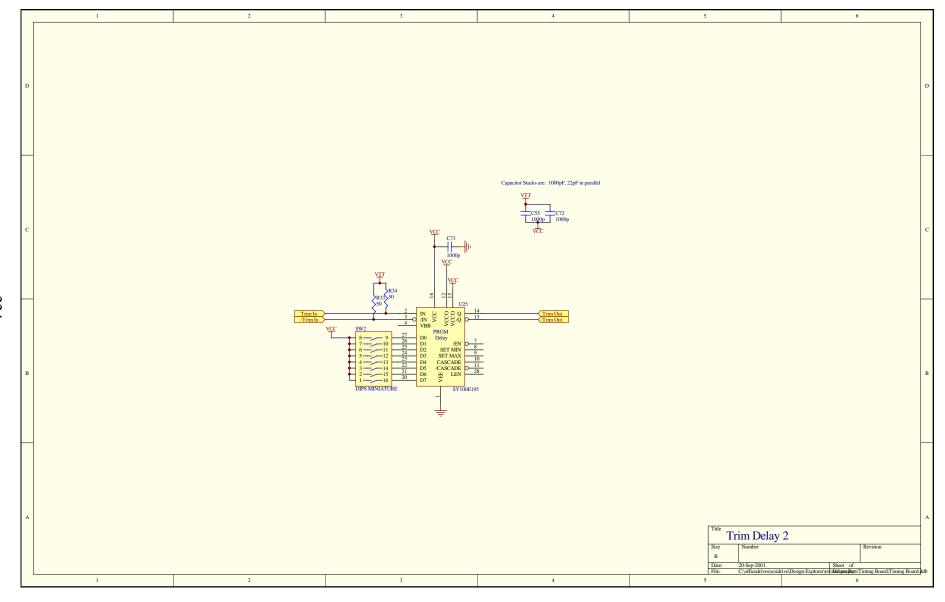

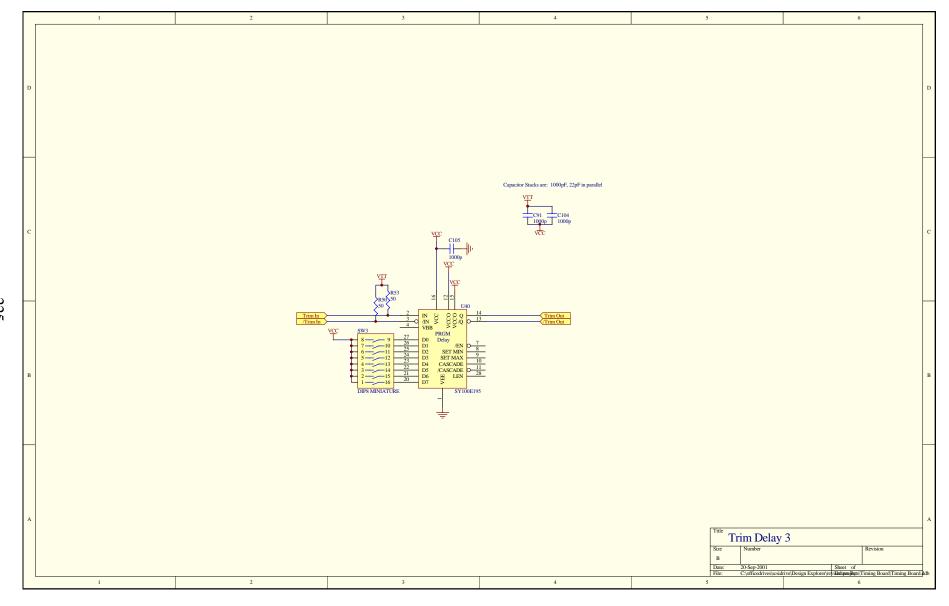

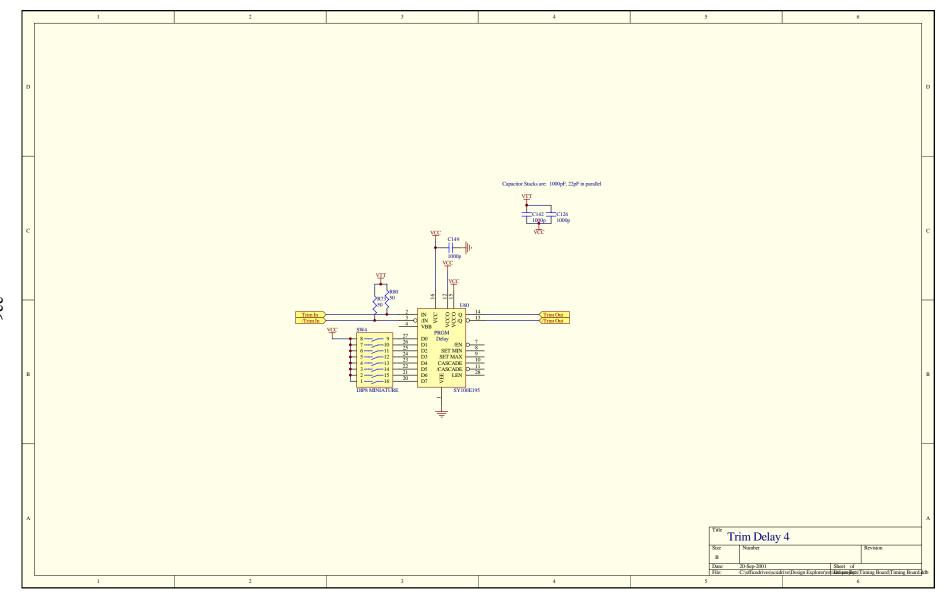

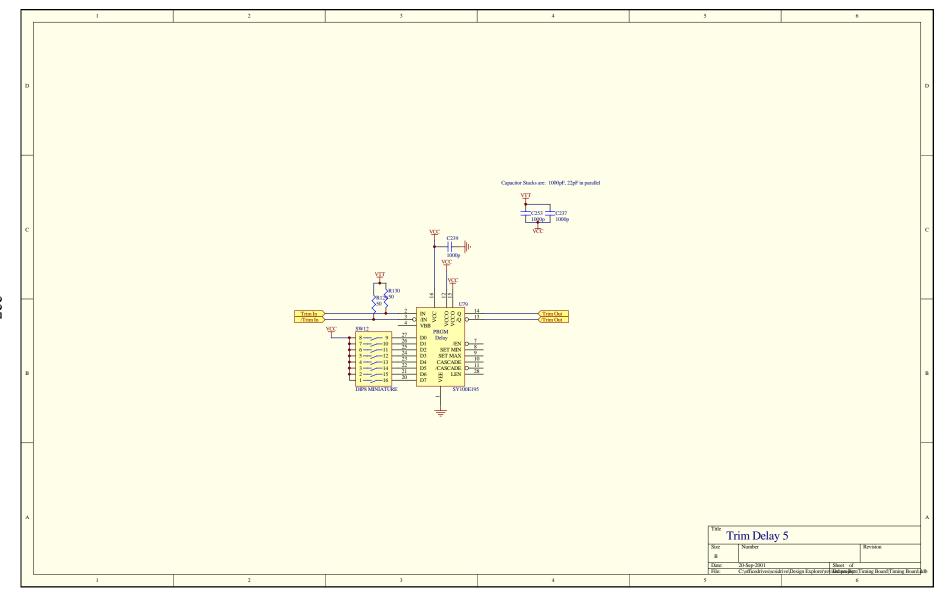

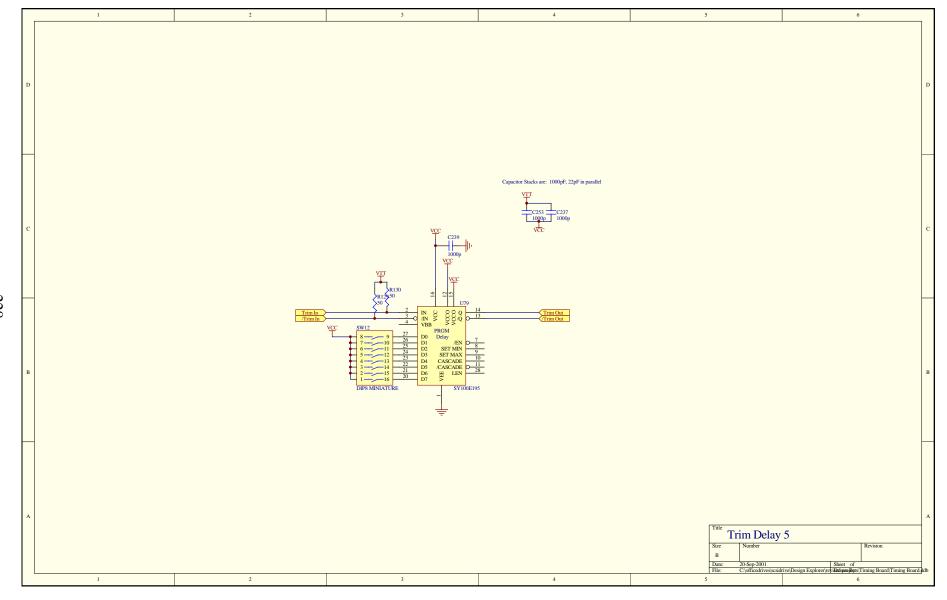

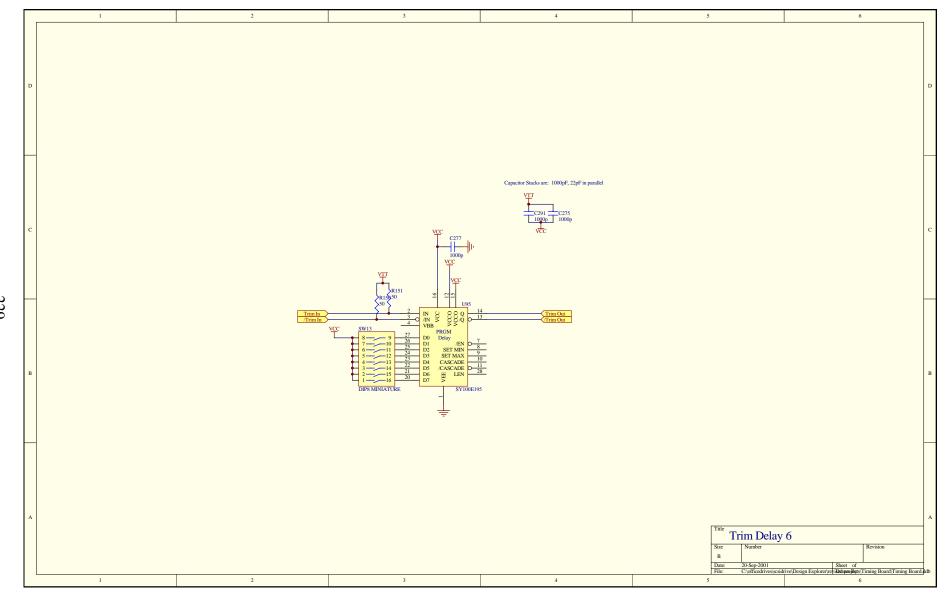

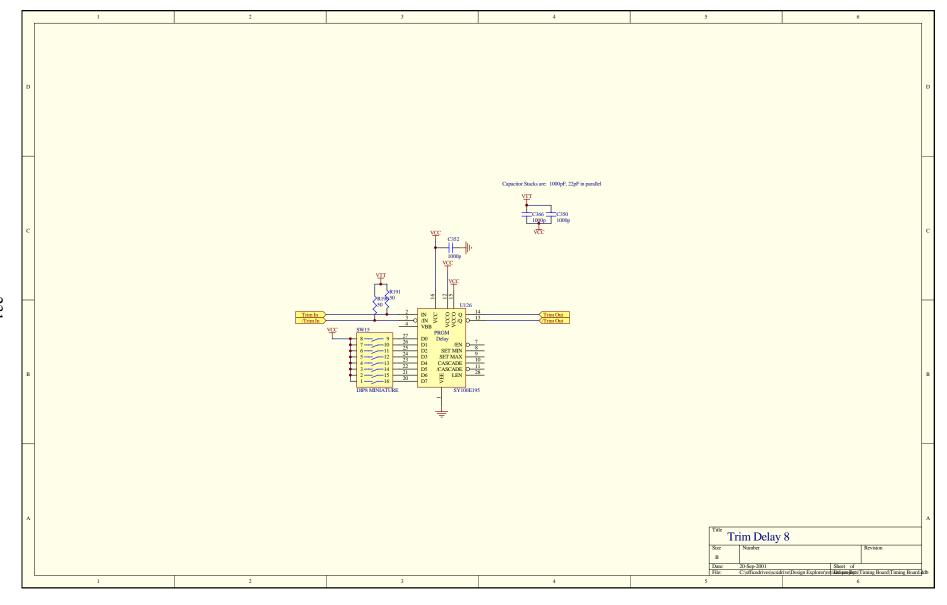

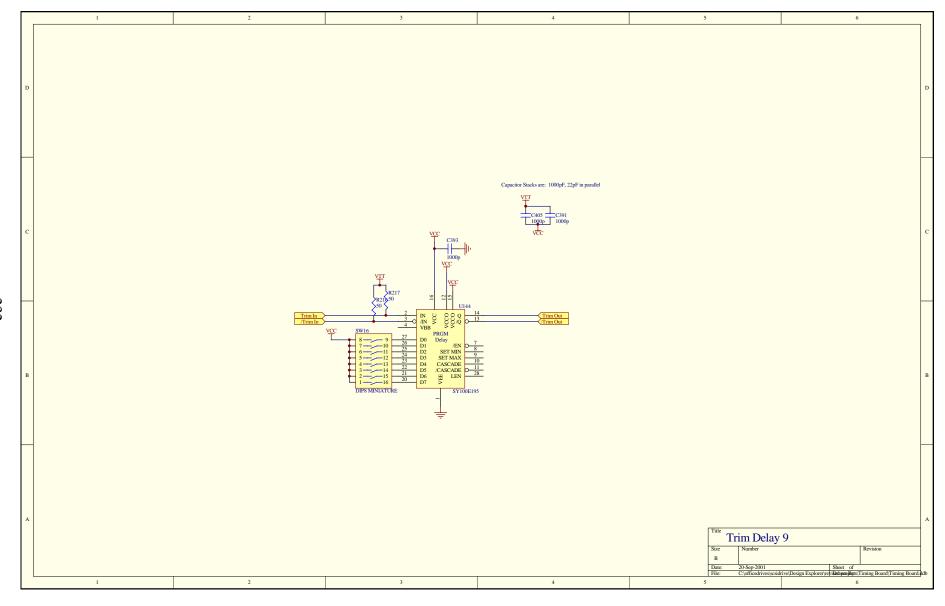

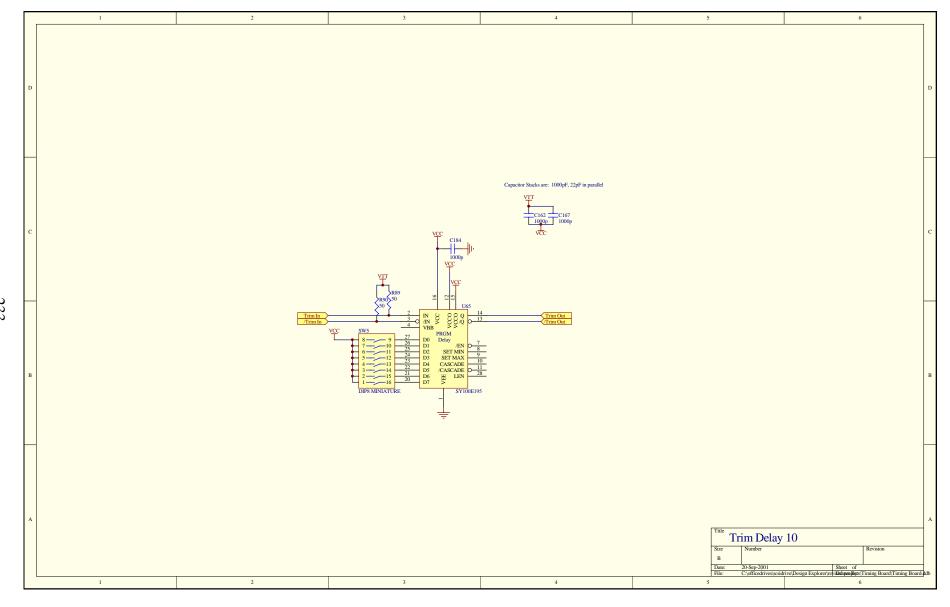

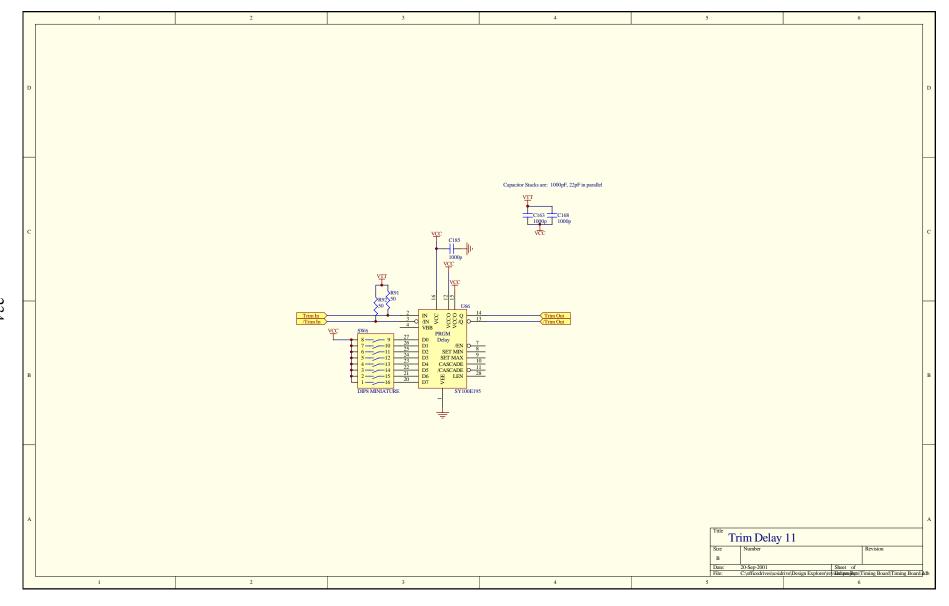

| Figure 4-15 Trim Delay Schematic                                      |       |

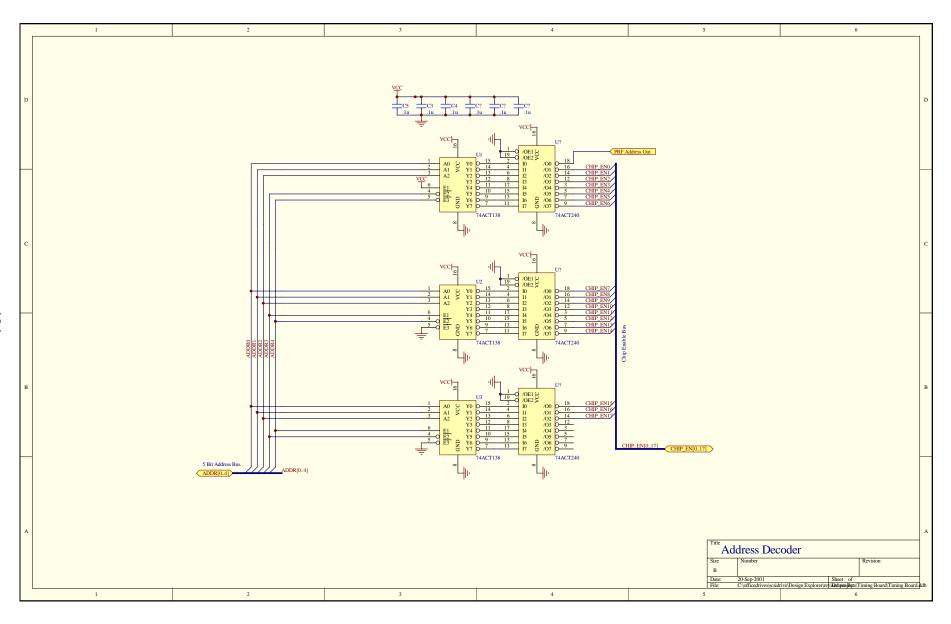

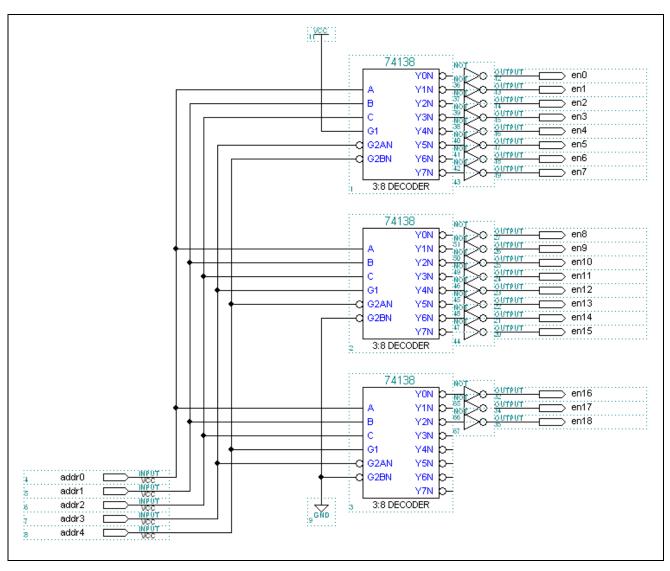

| Figure 4-16 Address Decoder Schematic                                 | . 104 |

| Figure 4-17 Mezzanine Microcontroller Connection Schematic            | . 105 |

| Figure 4-18 Mezzanine Card Board Stackup                              |       |

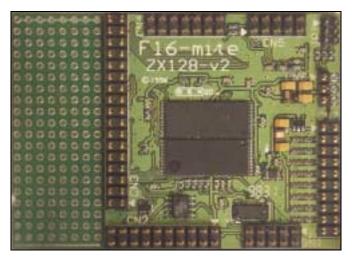

| Figure 4-19 Mezzanine Card Photograph                                 | . 106 |

| Figure 4-20 Mezzanine Card PCB Routing Style                          | . 107 |

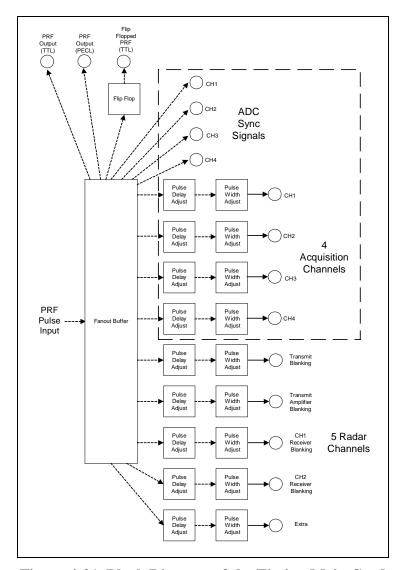

| Figure 4-21 Block Diagram of the Timing Main Card                     | . 109 |

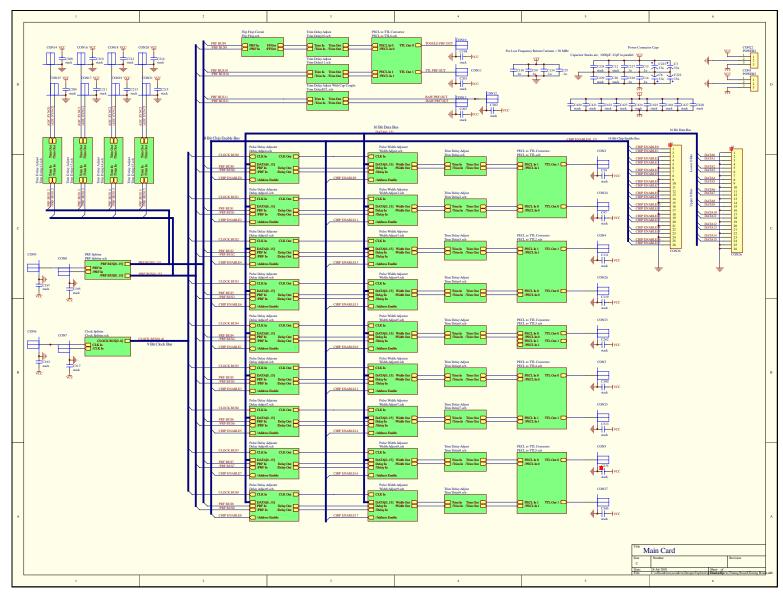

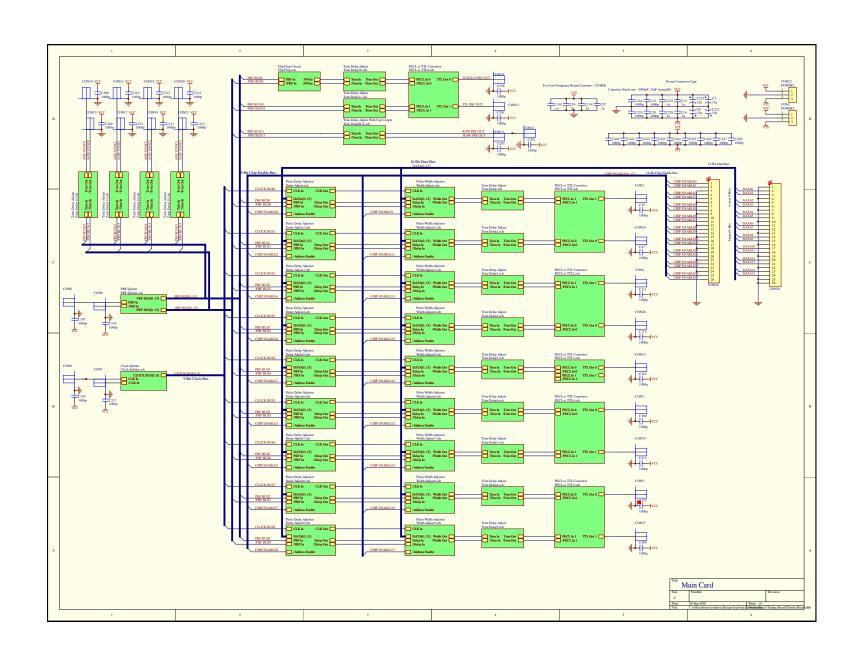

| Figure 4-22 Main Card Top Level Schematic                             |       |

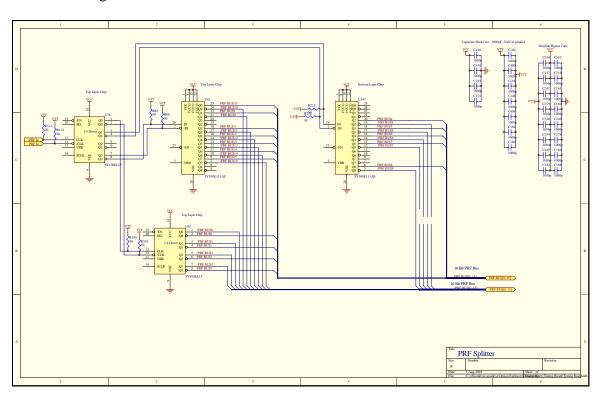

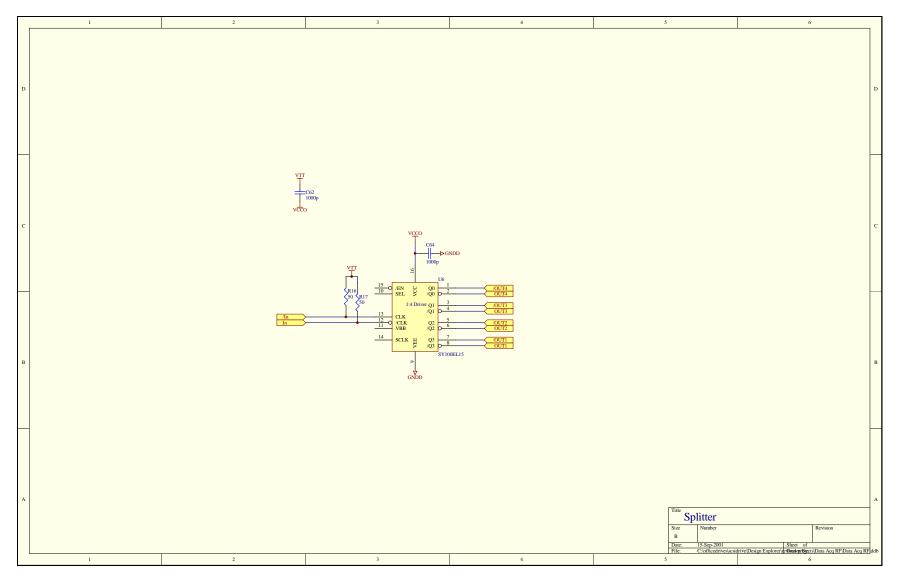

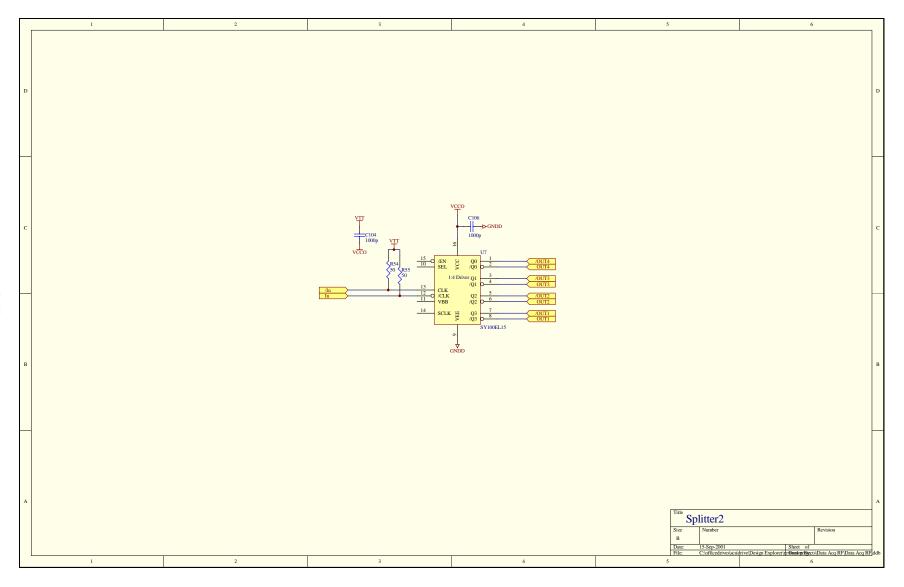

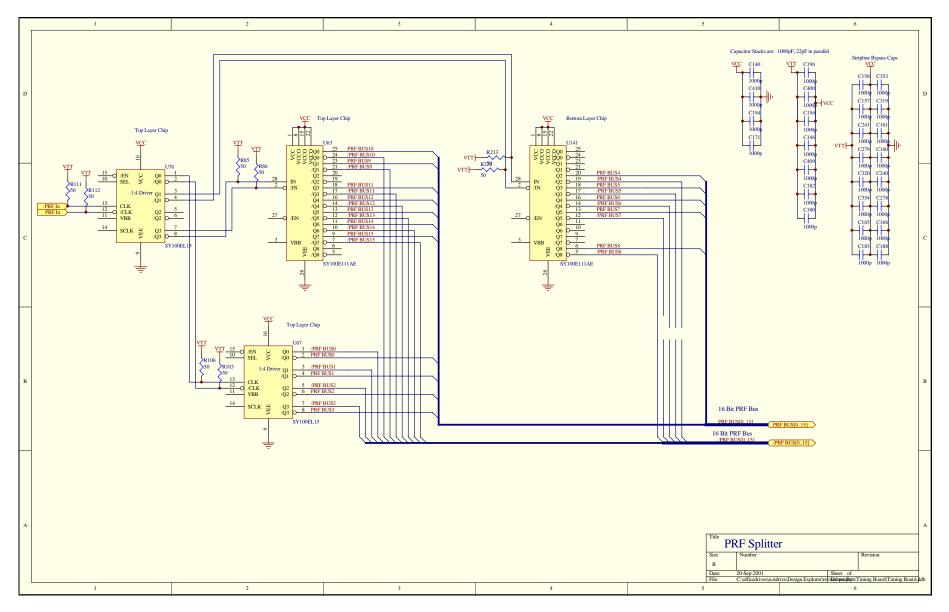

| Figure 4-23 PRF Splitter Schematic                                    |       |

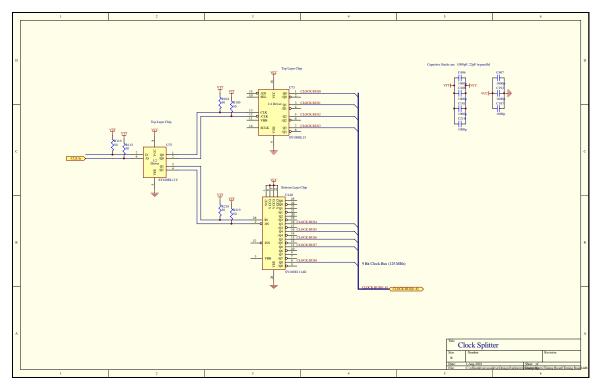

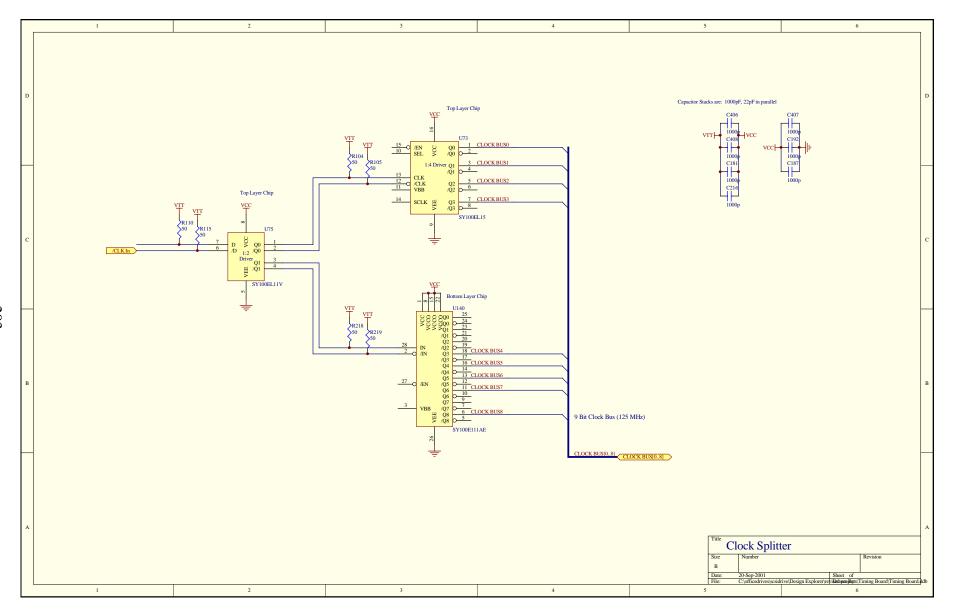

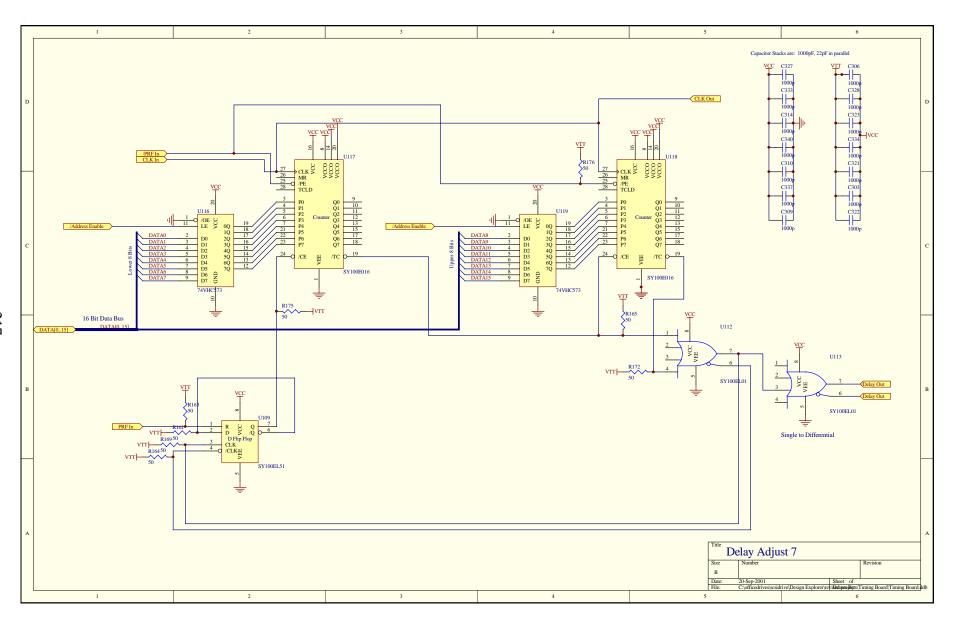

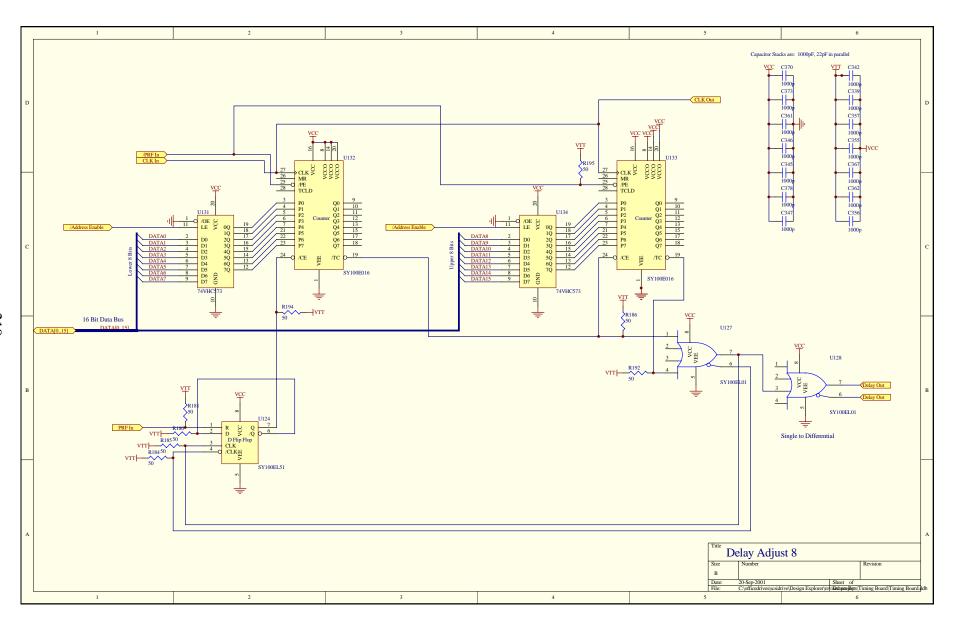

| Figure 4-24 Clock Splitter Schematic                                  |       |

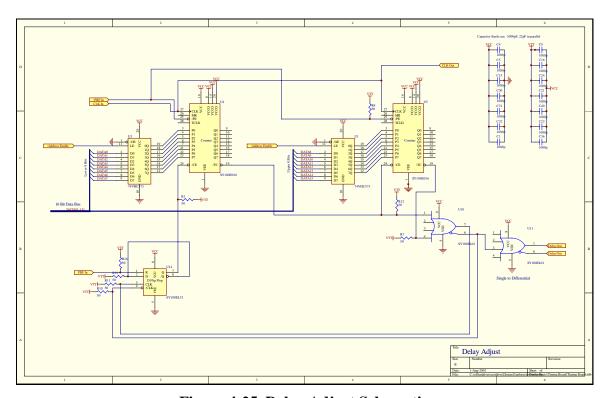

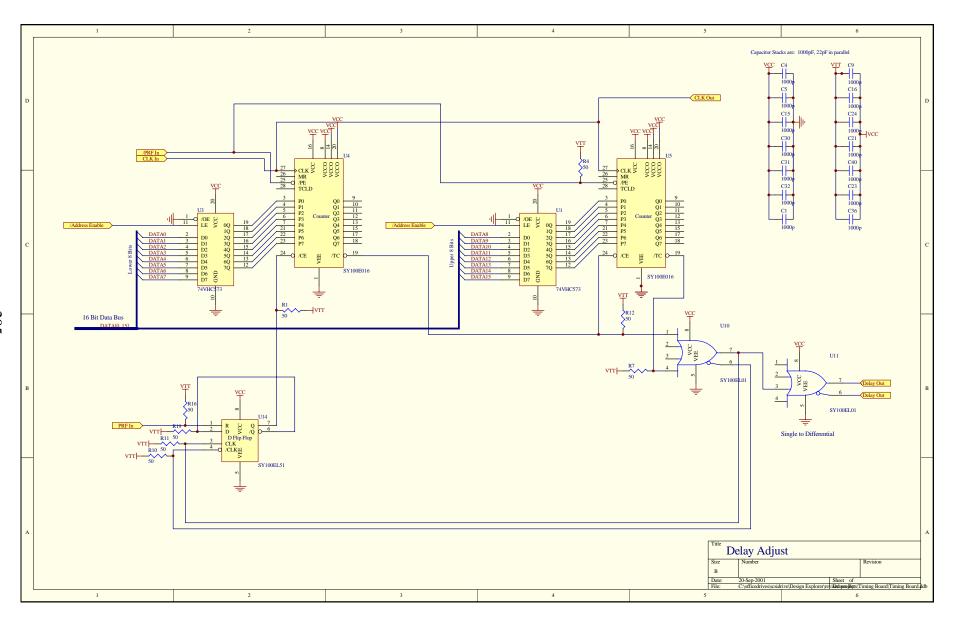

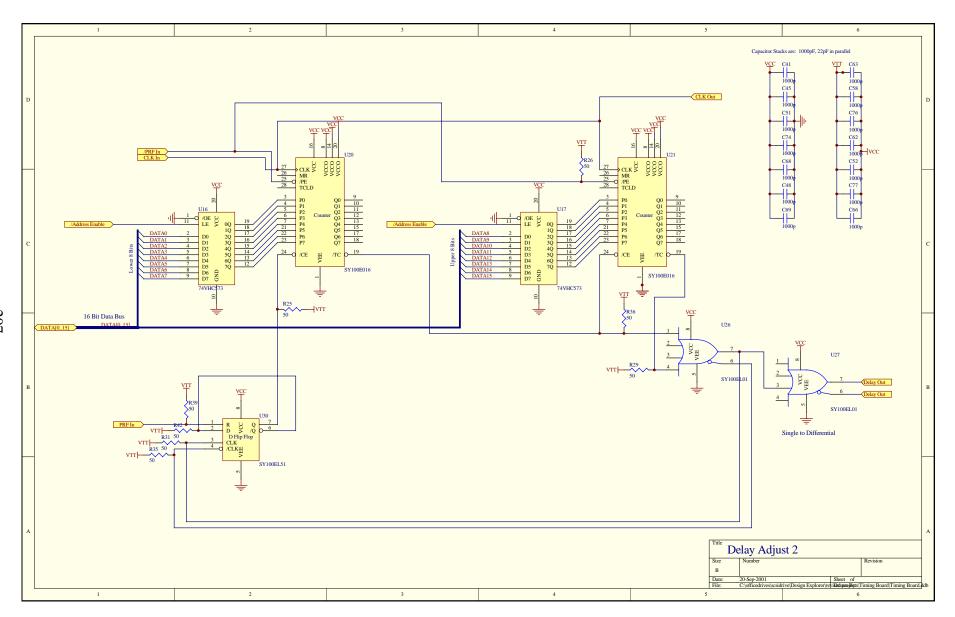

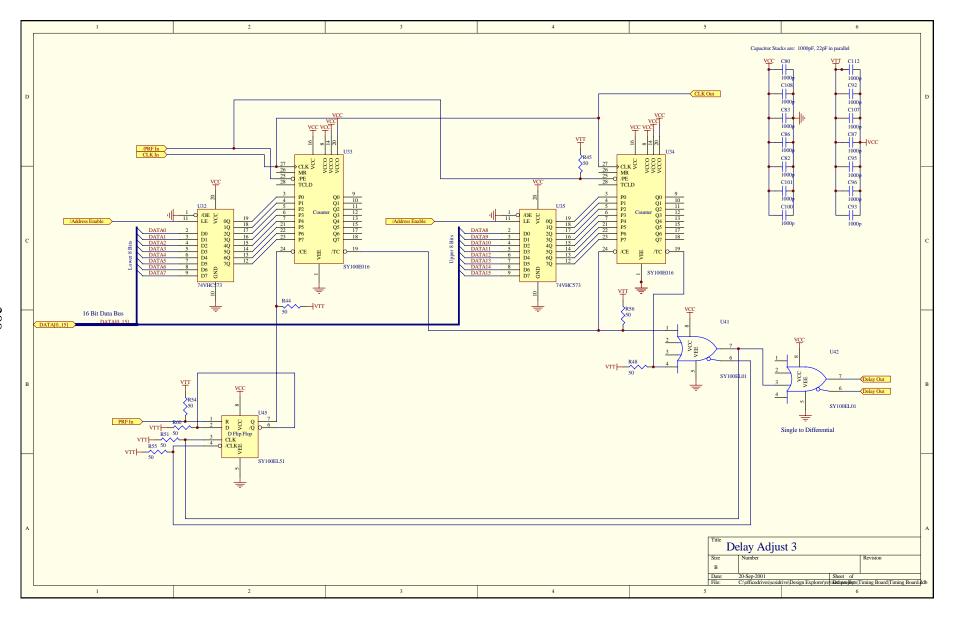

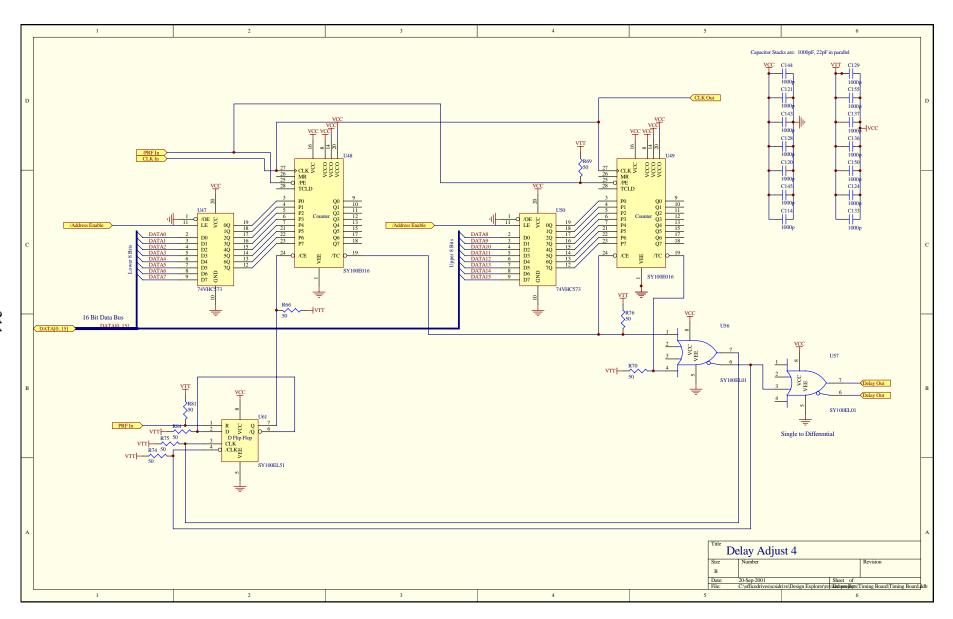

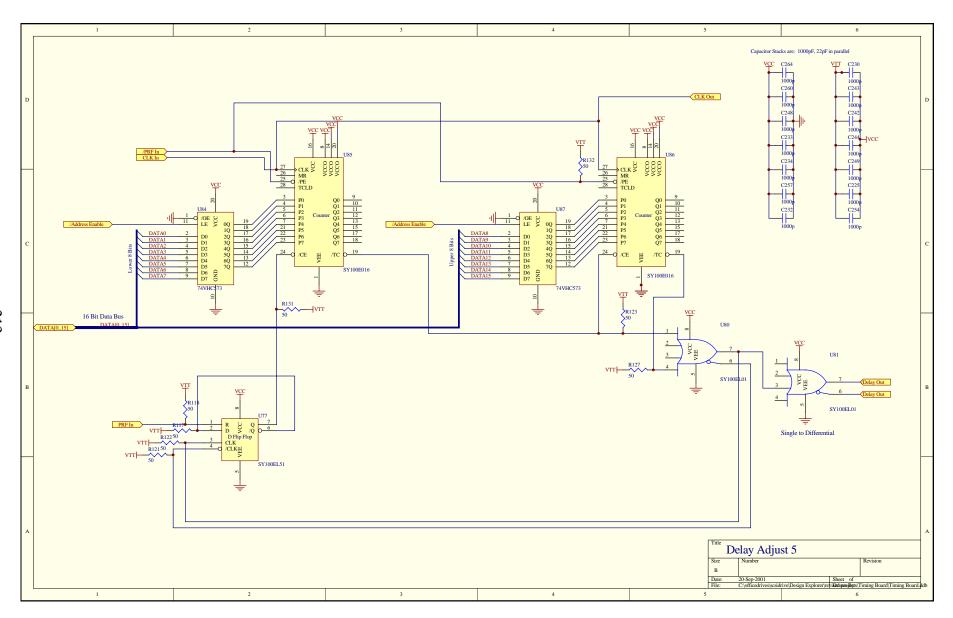

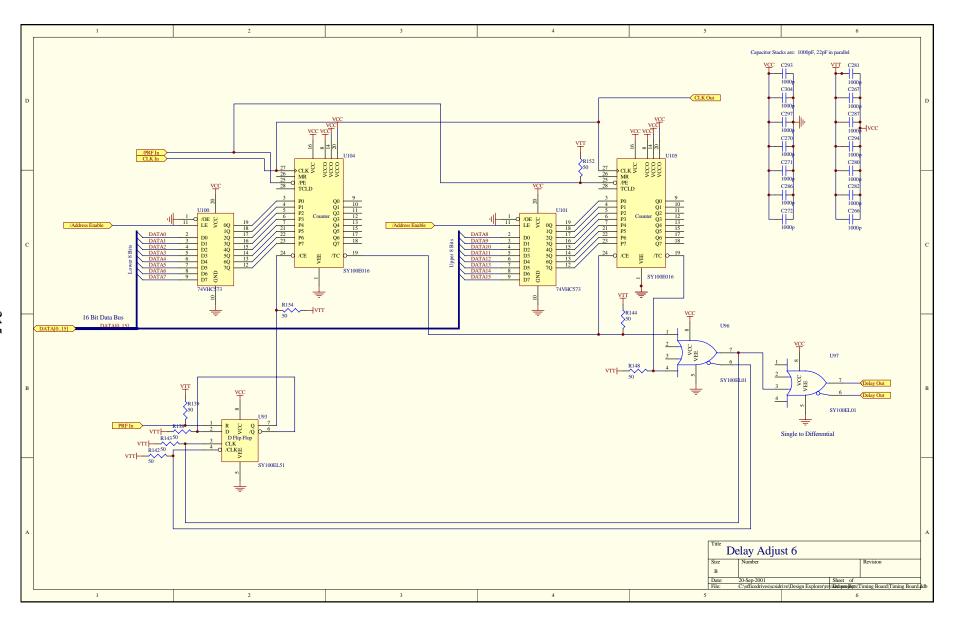

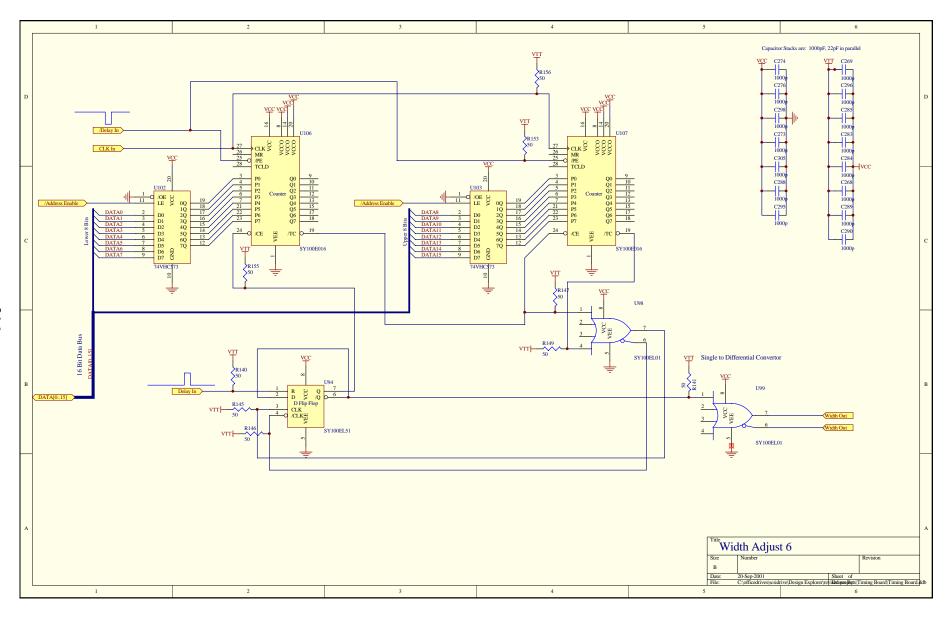

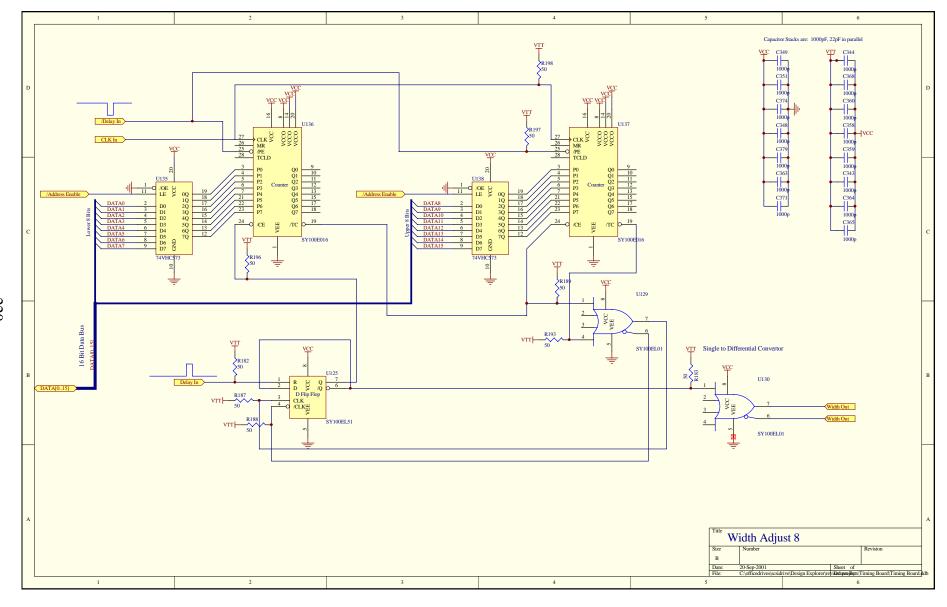

| Figure 4-25 Delay Adjust Schematic                                    |       |

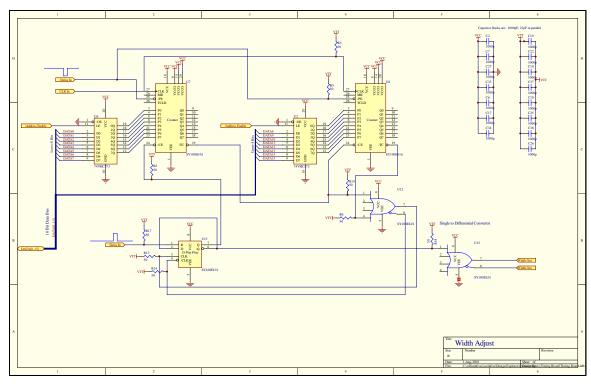

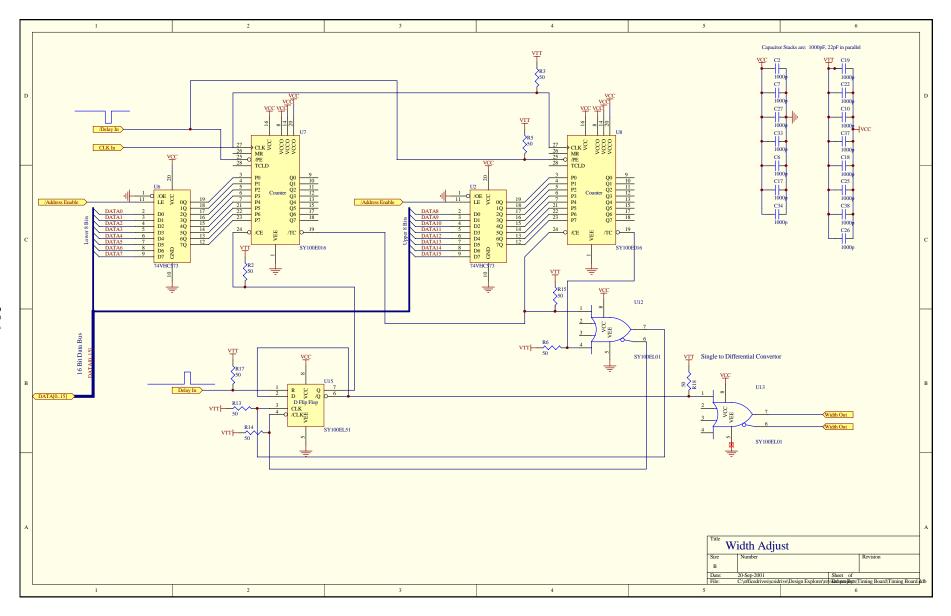

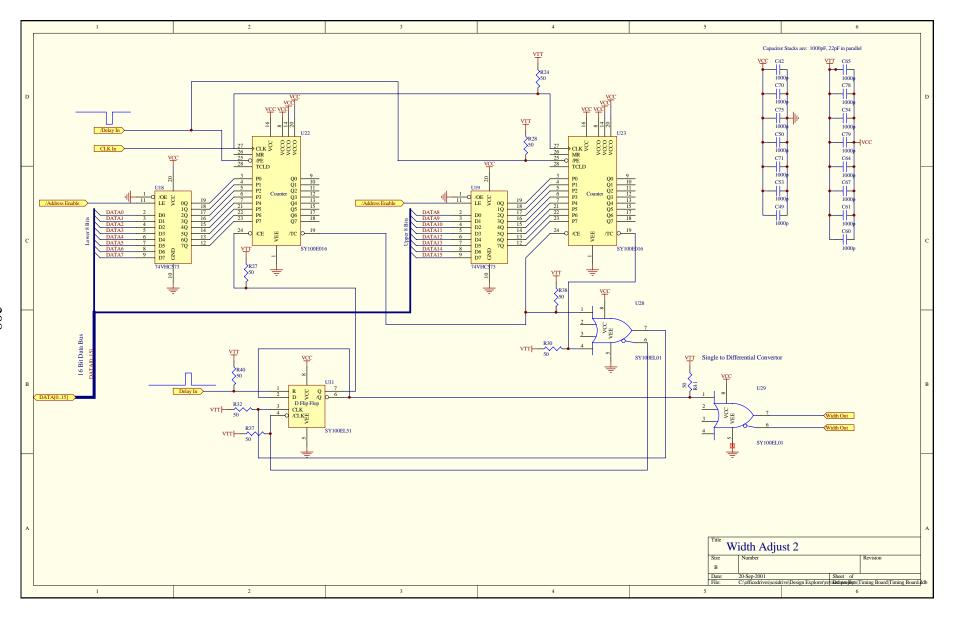

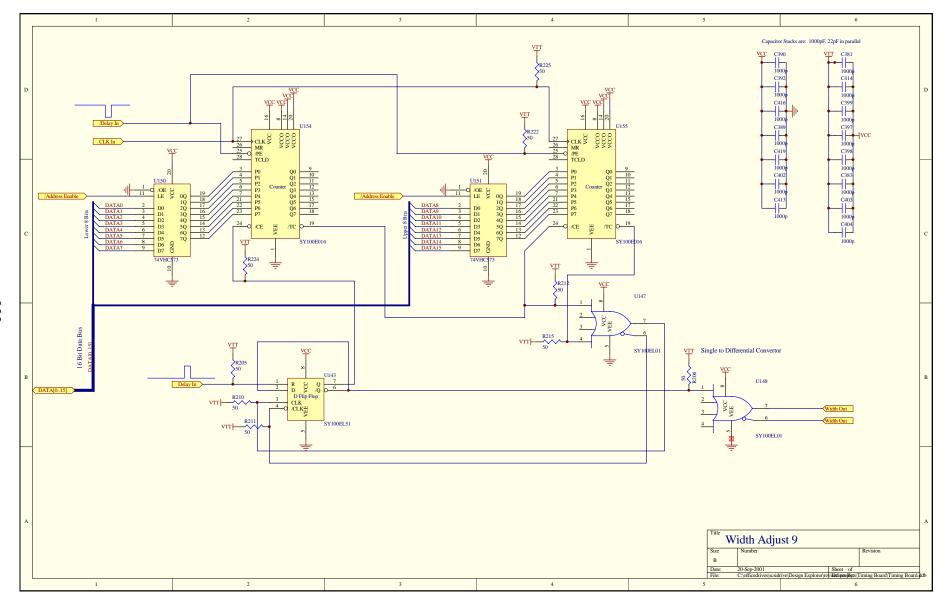

| Figure 4-26 Width Adjust Schematic                                    |       |

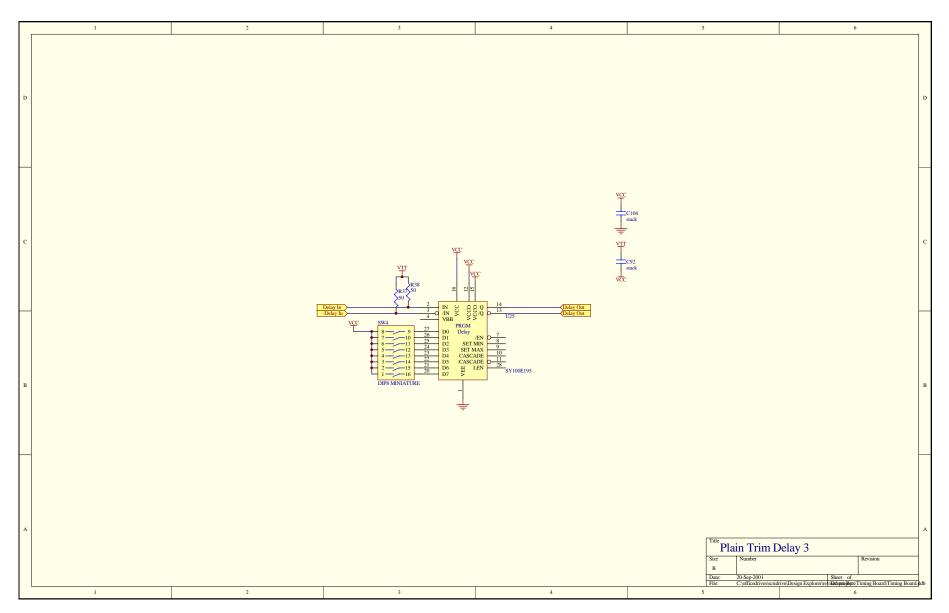

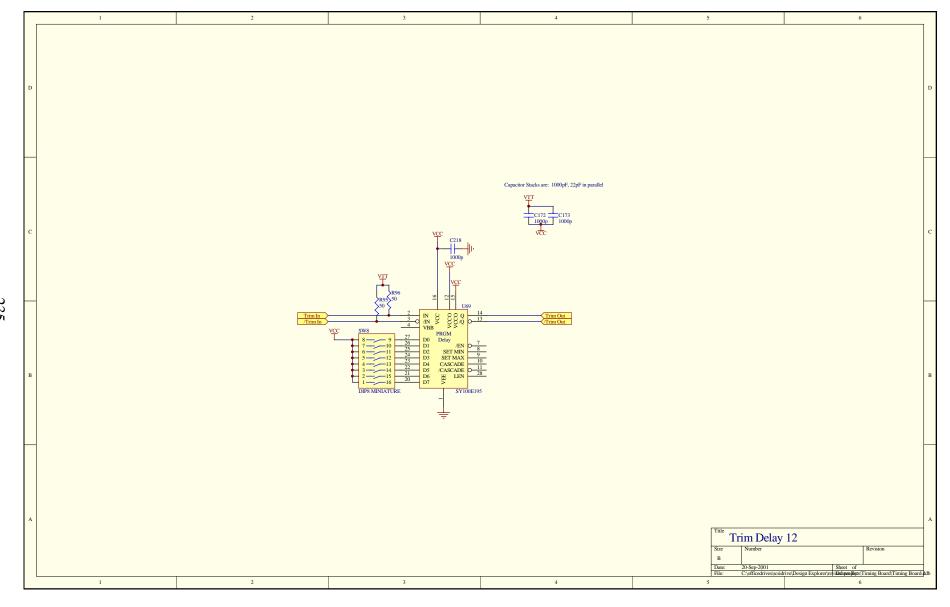

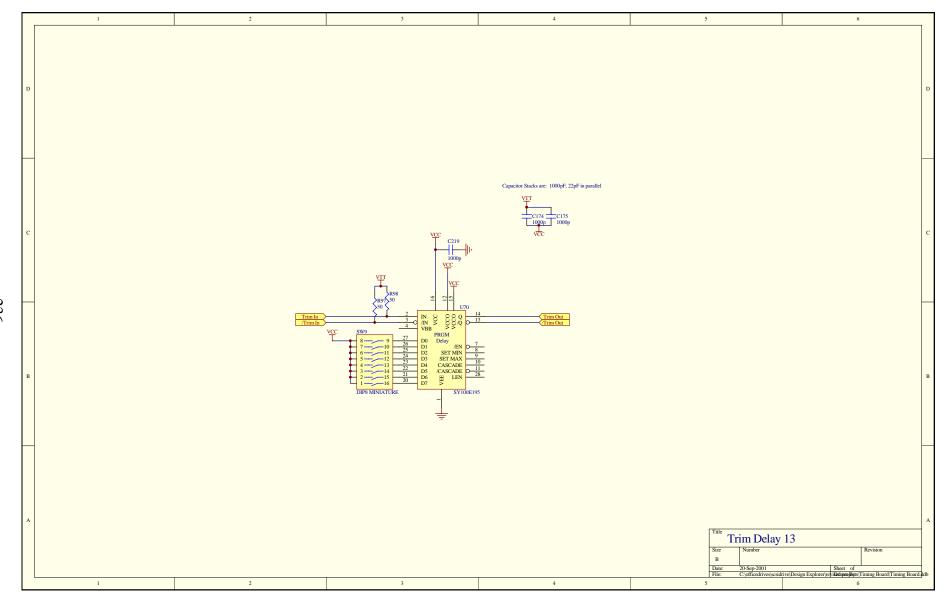

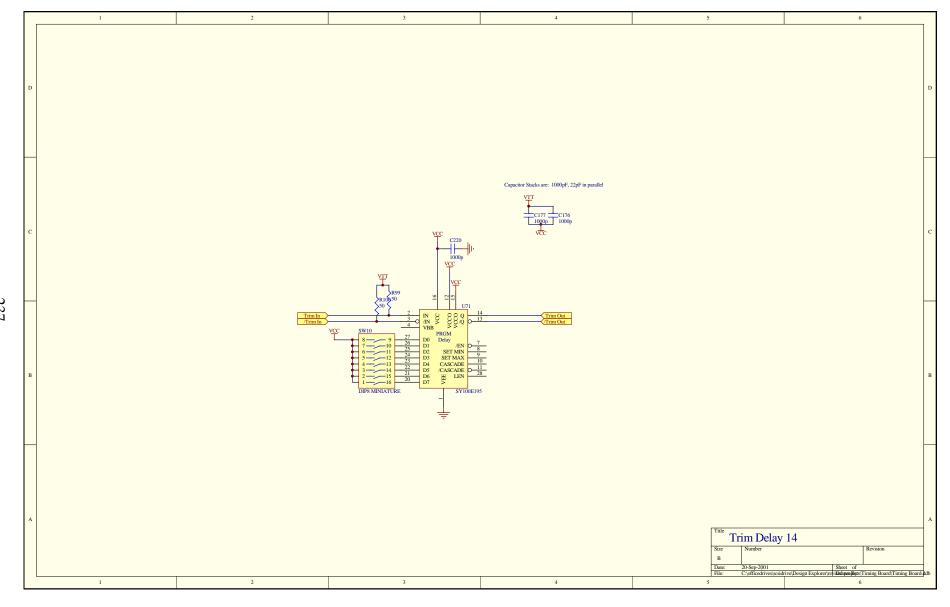

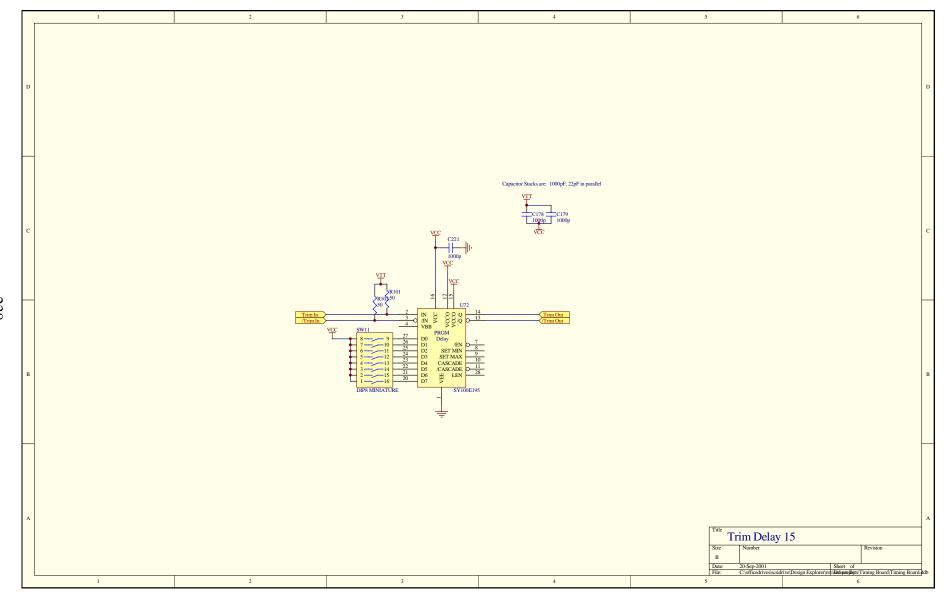

| Figure 4-27 Trim Delay Schematic                                      | . 118 |

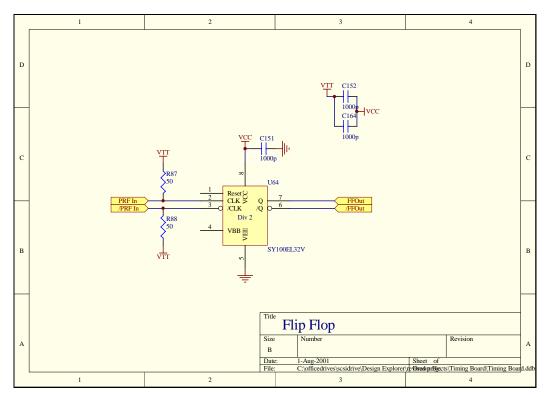

| Figure 4-28 Flip Flop Schematic                                       |       |

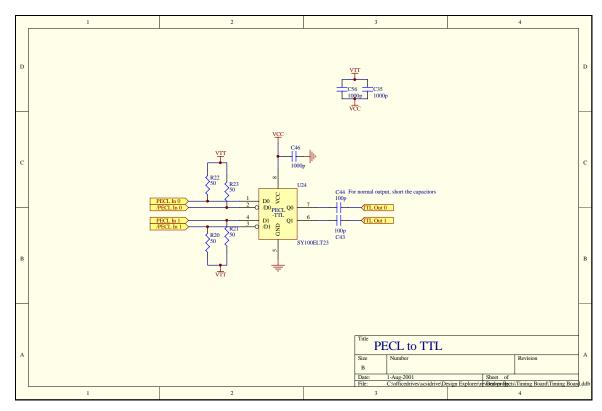

| Figure 4-29 PECL to TTL Schematic                                     |       |

| Figure 4-30 Main Card Stackup                                         | . 121 |

| Figure 4-31 Photograph of the Main Card                               |       |

| Figure 4-32 Timing System Microcontroller Photograph                  |       |

| Figure 4-33 Microcontroller Interface Schematic                       | . 126 |

| Figure 4-34 Microcontroller LCD Interface                             | . 127 |

| Figure 5-1 Interleaved ADC Clock Configuration                        |       |

| Figure 5-2 ECL-Sine Wave Converter Schematic                          |       |

| Figure 5-3 ECL-Sine Wave Converter Photograph                         |       |

| Figure 5-4 ADC Card Testing Diagram                                   |       |

| Figure 5-5 ADC Card Test Circuit Schematic                            |       |

| Figure 5-6 ADC Card Tester Photograph                                 |       |

| Figure 5-7 ADC Card Tester Output Waveform                            |       |

| Figure 5-8 Average Card Tester Schematic                              |       |

| Figure 5-9 Average Card Tester Photograph                             |       |

| Figure 5-10 ECL Terminator Photograph                                 |       |

| Figure 5-11 Oscilloscope Output of a 1-GHz PECL Signal                |       |

| Figure 6-1 Timing System Validation Setup                             |       |

| Figure 6-2 Timing System Divided Outputs With 2.4 GHz Input Frequency |       |

| Figure 6-3 ADC Card Validation Setup                                  |       |

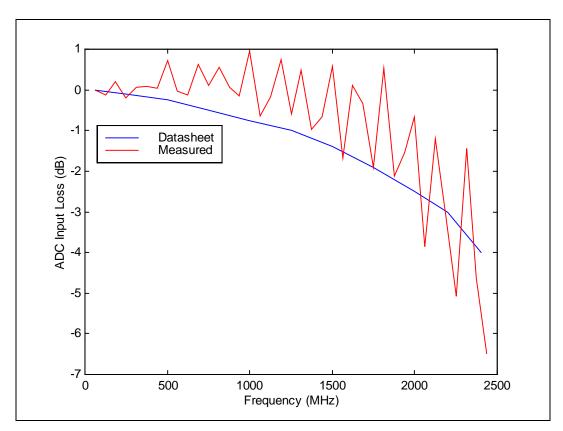

| Figure 6-4 Measured vs Datasheet ADC Analog Frequency Response        |       |

| Figure 6-5 Averaging Card Test Setup                                  |       |

| Figure 6-6 Complete System Test Setup                                 |       |

| Figure 6-7 System Time Domain Output with a 300-kHz Input             |       |

| Figure 6-8 System Frequency Domain Output with a 300-kHz Input        |       |

| Figure 7-1 FPGA Based Averaging Card Design                           |       |

|                                                                       |       |

## **List of Tables**

| <b>Table 2-1</b> | Histogram and Averaging for a Input Level of 131.576839   | 14  |

|------------------|-----------------------------------------------------------|-----|

| <b>Table 3-1</b> | Comparison of Intended and Actual Output Connector Pinout | 28  |

| <b>Table 3-2</b> | Serial and Parallel Load Pinouts of Connector J10         | 44  |

| <b>Table 3-3</b> | Processor Boot Configuration                              | 49  |

| <b>Table 3-4</b> | Correlation Between DSP and Temporal Sample Numbers       | 56  |

| <b>Table 3-5</b> | Output Multiplexer Circuit Switching Pattern              | 56  |

| <b>Table 4-1</b> | Timing System Address Map                                 | 104 |

| <b>Table 4-2</b> | Microcontroller Pinout                                    | 125 |

| <b>Table 4-3</b> | Microcontroller Interface Menus                           | 127 |

| <b>Table 4-4</b> | Valid Microcontroller Serial Commands                     | 128 |

| <b>Table 5-1</b> | Average Card Tester Output                                | 135 |

| Table 6-1        | ADC Frequency Response Data                               | 142 |

|                  |                                                           |     |

#### CHAPTER 1 INTRODUCTION

To more accurately determine the role of glacier ice systems in sea level rise, glacier accumulation rate measurements are needed. Historically, this information has been gathered using core samples collected at various points on a glacier resulting in an accumulation rate measurement error of 20 to 24 percent [1]. For improved accuracy, remote sensing techniques are required to improve temporal and spatial coverage of accumulation measurements.

During the summers of 1998-99, the University of Kansas Radar and Remote Sensing Laboratory (RSL) operated a prototype ground based frequency modulated continuous wave (FMCW) radar on the Greenland ice sheet. Results from the prototype demonstrated a long-term accumulation measurement error of less than 5 percent. The results also showed the optimum frequency of operation for an accumulation radar was 500 to 1000 MHz [1]. Based on these results, it was desired to build an airborne pulse radar operating from 600 to 900 MHz. This project was the first attempt at building a wide bandwidth radar data acquisition system for this high-resolution radar.

The enabling technology for this system is the introduction of gigahertz speed analog to digital converters (ADCs) onto the consumer market. The converters selected for this project can directly digitize signals with frequencies as high as 2.2 GHz with bandwidths up to 500 MHz. The immediate goal of the acquisition system was to directly digitize the accumulation radar output using a single acquisition channel. A single acquisition channel is crucial for a high resolution radar because it eliminates the

need for quadrature demodulation which creates spurious components in the radar analog output resulting in ghost images in the processed data.

The final system consists of a computer system and five unique circuit boards: ADC Card, Averaging Card, Multiplexer Card, Timing Main Card, and Timing Mezzanine Card. The ADC Card samples the radar analog signal at up to 1 Gsample/sec and outputs digital signals in sixteen 8-bit streams. The Averaging Card buffers those digital streams and performs a coherent averaging algorithm using four digital signal processors. The Multiplexer Card is used to switch multiple acquisition channels into a single channel for transfer to the acquisition computer. The final two boards (Main Card and Mezzanine Card) create a precision timing system that is required to maintain coherency with system clock speeds of 1 GHz.

In this project, each of the five circuits was designed and constructed. The timing system was completed and shown to work with clock frequencies as high as 2.4 GHz. The ADC Card was also validated and shown to have a frequency response similar to the manufacturers ratings up to 2.2 GHz. The Averaging Card concept was validated but the circuit could not be made to work properly due to manufacturability issues. The board's functionality was correct but the DSP's were found to operate intermittently either due to a solderability problem or inability to implement "jumper wire" changes. It is believed that this board would operate if a PCB revision was implemented. The Multiplexer Card was shown to work although the full capabilities could not be tested without fully functional Averaging Cards.

Chapter 2 is a review of the theory necessary to understand the full potential of this wide bandwidth acquisition system. Chapter 3 is a detailed description of the ADC

Card, Averaging Card, Multiplexer Card, and computer interface. Chapter 4 is a detailed description of the precision timing system including the Main Card, Mezzanine Card, and timing system microcontroller. Chapter 5 is a description of special test and measurement circuits that were built for system validation and debugging. Chapter 6 presents laboratory measurement results. Chapter 7 presents conclusions and recommendations for further development.

#### CHAPTER 2 THEORY AND CONCEPTS

In order to understand the full potential of the ADCs used in this project, a complete understanding of the Nyquist sampling theorem and ADC characteristics is required. This chapter is an overview of these fundamentals.

#### 2-1 Nyquist Sampling Theorem Review

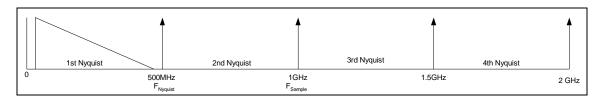

The Nyquist sampling theorem defines the frequency domain limits for a sampled signal versus the sampling frequency. The most common interpretation of the theorem is that the sample frequency must be greater than twice the highest analog frequency to be digitized. Once the sample rate has been defined, the frequency spectrum can then be broken into "Nyquist zones" where each zone has a bandwidth equal to half the sample frequency. This is shown graphically in Figure 2-1 with an arbitrary signal present in the first Nyquist zone. By the previous definition, any signal falling into the first Nyquist zone can be precisely reconstructed.

Figure 2-1 Frequency Domain of Traditional Sampling

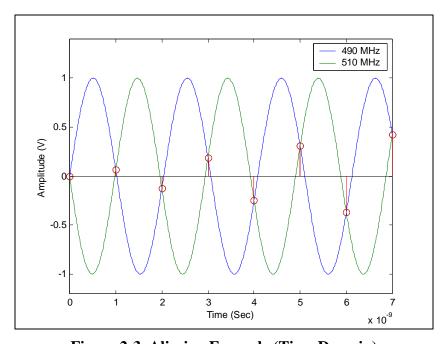

If the bandwidth of the analog signal of Figure 2-1 is allowed to increase into the second Nyquist zone, the signal cannot be reconstructed. This effect is called aliasing and is shown graphically in Figure 2-2. As seen in the figure, any signals present in the second Nyquist zone will "fold backwards" into the first Nyquist zone and add to the signals already present. A time domain example of aliasing is shown in Figure 2-3. In

that figure, a 490-MHz sine wave and a 510-MHz sine wave produce identical samples when the Nyquist frequency is 500 MHz. The figure clearly shows that <u>once an analog signal is digitized</u>, it is impossible to determine which Nyquist zone it came from. In practice, aliasing can be eliminated by attenuating all frequencies outside the first Nyquist zone. The filter must attenuate unwanted signals until their amplitude is below the noise floor of the ADC [2]. This is called an antialiasing filter and is present in most real-world acquisition systems.

Figure 2-2 Aliasing Example (Frequency Domain)

Figure 2-3 Aliasing Example (Time Domain)

The previous definition of the Nyquist theorem is only a partial application of the theorem. A broader definition would be that in order to perfectly reconstruct an analog signal, the following three conditions must be met:

- 1. The sampling rate must be at least twice the bandwidth of the analog signal.

- 2. The analog signal must lie entirely within a single Nyquist zone.

- 3. The original Nyquist zone must be known during reconstruction.

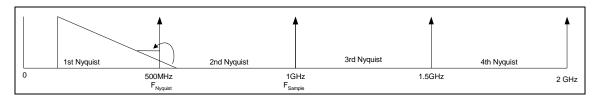

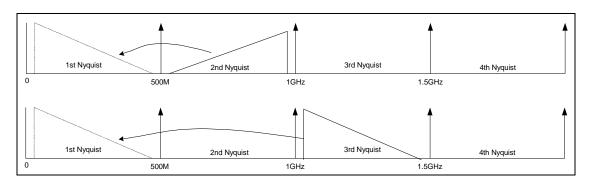

By this definition, a signal does not have to be in the first Nyquist zone. For example, if a signal lies entirely within the second Nyquist zone, the signal's spectrum will "fold back" into the first Nyquist zone after sampling but all necessary information is retained. This is shown graphically in Figure 2-4. Note from the figure, that any Nyquist zone may be used although even zones produce a "frequency folding" effect where odd Nyquist zones have only a "frequency shifting" effect. This "frequency shifting" effect is equivalent to downconversion and is highly desirable in many radar and radio applications. This type of sampling outside the first Nyquist zone is called "undersampling" or "bandpass sampling." When it is used for a downconversion application it is called "direct downconversion" [2].

Figure 2-4 Undersampling from Even and Odd Nyquist Zones

Special ADCs must be designed for undersampling. Ordinary ADCs are designed strictly to operate in the first Nyquist zone. The frequency response of the analog input section of the ADC normally rolls off rapidly above the Nyquist frequency to reduce the

requirements of the antialiasing filter. Because of this, undersampling even in the second Nyquist zone is not possible. Special ADCs with an analog bandwidth that extend into multiple Nyquist zones are necessary for undersampling applications. The MAX104 ADCs chosen for this project have a Nyquist frequency of 500 MHz with an analog bandwidth of 2.2 GHz thus enabling undersampling into the 5<sup>th</sup> Nyquist zone.

Assuming direct downconversion is not desired, additional post-processing is necessary to recreate a signal after undersampling. Following the previous example (from Figure 2-4), with the knowledge that this signal came from the second Nyquist zone, reconstruction is a two-step process. First, an interpolation filter must be applied to double the sample frequency. Next, the signal is moved back to its original frequency band by either folding across 500 MHz in the frequency domain or by multiplying with a 500-MHz sine wave in the time domain.

#### 2-2 Limitations and Characteristics of Real Analog-to-Digital Converters

The first and most obvious limitation of a real ADC is quantization. Real ADCs can be purchased with output resolutions ranging typically from 6 to 16 bits. The effect of quantization is to raise the noise floor in the digital domain thus increasing the amplitude of the smallest signal that can be discerned. The performance measure used to characterize this is the signal-to-noise ratio (SNR). The SNR of an ideal ADC is calculated using the following formula [2]:

$$SNR = 6.02B + 1.76 + 10\log_{10}\left(\frac{f_s}{2f_{\text{max}}}\right)$$

(1)

where,

B =number of converter output bits, no units

$f_s$  = sample frequency, Hz

$f_{max}$  = maximum frequency of a lowpass input, Hz

Ignoring the frequency dependent term for now (discussed below), the SNR is directly proportional to the number of output bits. Using the equation, an ideal 8-bit ADC has a maximum SNR of 49.9 dB. This SNR is only achieved with a full scale input. For amplitudes less than full scale, the quantization step size becomes a larger percent of the signal and the SNR is degraded. In practice, real ADCs will approach this value but fall short by 2 to 5 dB due to analog limitations, thermal noise, and non-linearity in the conversion process.

Real ADCs are sometimes rated using the effective number of bits (ENOB). This is the number of bits of an ideal ADC (found using the equation 1) necessary to produce the SNR of the real ADC. For example, the MAX104 8-bit ADC achieves an SNR of 47.4 dB which is an ENOB of 7.74 bits.

The frequency dependent term of (1) applies to one special case and actually allows the ENOB to increase beyond the normal rating of the converter. This term applies for the case of oversampling (when the sample frequency (bandwidth) is much greater than the minimum frequency specified by the Nyquist theorem). Oversampling improves performance because the quantization noise has a fixed amount of power. As the sample rate is increased, the quantization noise is spread over a larger bandwidth. By applying digital filtering that passes only the desired signal, some of the quantization noise power is removed. Without this special processing, the SNR does not improve because the full quantization noise power is still present in the sampled waveform. With this special technique, an 8-bit ADC, sampling a 100 kHz signal at 20 MHz can provide an SNR of 68 dB resulting in an ENOB of 11 bits [2].

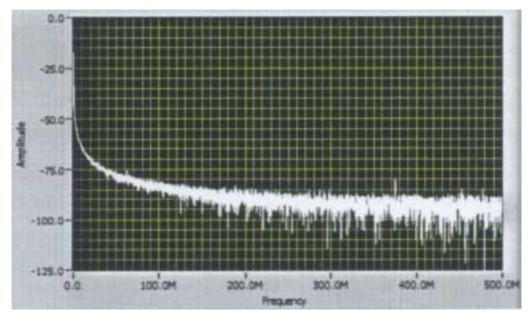

One additional rating of a real ADC is the spurious free dynamic range (SFDR). The SFDR is measured by inputting a very pure sinusoid into the ADC an observing the fast Fourier transform (FFT) of the output data. The FFT will contain a single large impulse representing the sine wave, but will also contain smaller impulses that extend above the noise floor. These smaller impulses are generally due to non-linearities in the conversion process [2]. The SFDR is then the difference (in dB) between the sine wave and the largest spurious component. An example of SFDR can be seen graphically at the bottom of Figure 2-6. For wideband applications, the SFDR will limit the difference between the largest and smallest signals that can be received because it is difficult to discern between a tiny signal and the spurious component of a large signal.

#### 2-3 Interleaving of Analog-to-Digital Converters

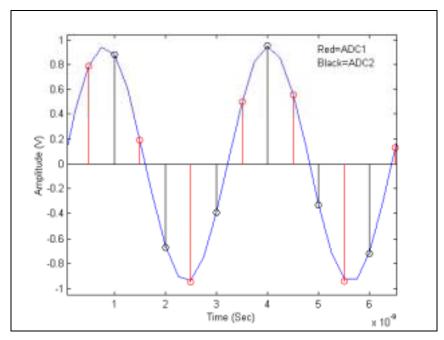

For ADCs with analog bandwidth extending into multiple Nyquist zones, interleaving of multiple converters can be used as an alternative to undersampling of high frequency signals. With interleaving, the analog waveform is sampled by multiple converters, each with a unique sampling phase, and the converter digital output streams are then combined together to effectively increasing the sample rate. Examples of this are two converters sampling at 0° and 180° to double the sample rate or four converters sampling at 0°, 90°, 180° and 270° to quadruple the sample rate. A time domain representation of two converter interleaving is shown in Figure 2-5.

Figure 2-5 Time Domain Example of Two Converter Interleaving

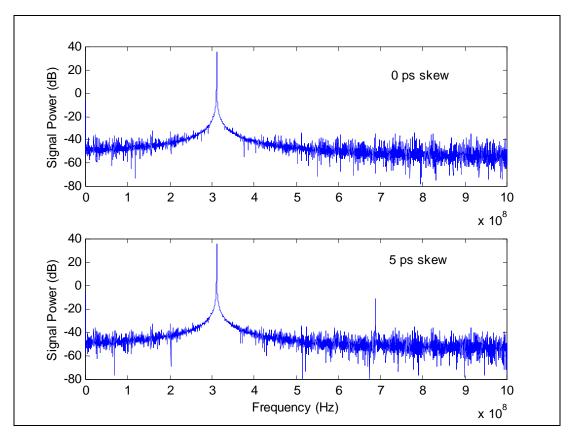

Theoretically, interleaving should produce results identical to a single high speed converter. Based on the high-speed characteristics of real ADCs it would seem interleaving would produce better results than a single converter since the interleaved converters operate at lower individual speeds. In practice, interleaving introduces spurious components because the two channels cannot be precisely matched in amplitude or phase. As the frequency of the input waveform and sample clock increases, the timing requirements to prevent these spurious components become evermore stringent. Figure 2-6 shows the output of a Matlab simulation illustrating the effects of even a slight phase offset when interleaving with converters operating at 1 GSPS with an input frequency of 310 MHz.

Figure 2-6 Spurious Components due to Mismatched Interleaving

As seen in the figure, an SFDR of 70 dB is achieved with perfect 180° timing. With the interleaved clock skewed by only 5 ps (1.8°) from the ideal value, the SFDR is reduced to 46 dB as a spurious component is mirrored across the Nyquist frequency (500 MHz). Using the same simulation it can be shown that a 1% difference in amplitude gain of the ADC's has a nearly identical effect. Surprisingly, the simulation shows that having a DC offset of a few LSBs on one channel does not create spurious components and only adds to the DC value of the interleaved signal (which can be easily removed during post processing).

In practice, it may be possible to achieve less than 5 ps clock skew through calibration but it would be extremely difficult to hold that calibration for any meaningful amount of time. Therefore, interleaving at very high speeds with the intent of increasing

the digitized bandwidth is not practical without sacrificing SFDR or applying special post processing to compensate for non-uniform sampling (algorithms for this are discussed in [3] and [4]). If the input signal is confined within a Nyquist zone, all spurious components can be filtered out during post processing and thus the side effects of interleaving are eliminated.

If the signal lies inside of a Nyquist zone, it is not necessary to interleave but interleaving does have three advantages in that situation. First, post-processing is simplified versus undersampling, requiring only a bandpass filter instead of interpolation and shifting in the frequency domain. Second, the SNR is improved by around 3 dB (for two converter interleaving) since half of the quantization noise will be filtered out by the bandpass filter operation [2]. Third, the system is more reliable since redundant data are being recorded. If one of the converters fails during acquisition, the data can still be recovered by treating the remaining converter stream as an undersampled signal.

#### 2-4 Coherent Averaging of Radar Signals

The dynamic range of an ADC is significantly improved if a measurement can be taken multiple times in the presence of noise. The basic theory behind coherent averaging is that if a signal is repetitive and the ADC is coherent to that signal, it can be sampled at exactly the same locations for each repeated measurement. The repeated measurements will then be identical except for random noise. This is shown graphically in Figure 2-7. From the figure, it is seen that the ensemble average (of a given sample number) of a coherent (noisy) waveform is equivalent to sampling a DC voltage in the presence of noise.

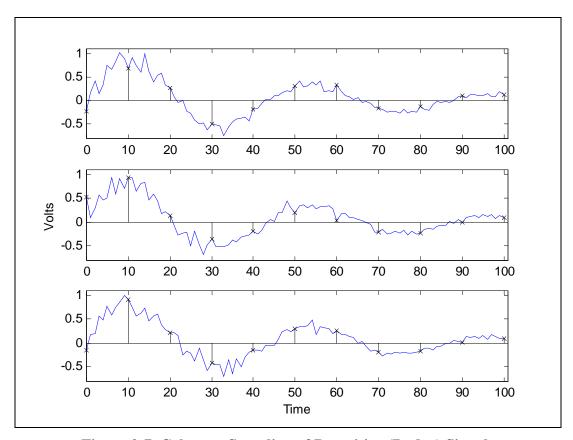

Figure 2-7 Coherent Sampling of Repetitive (Radar) Signals

The precision gain due to averaging is illustrated in the following example. Assume a DC voltage is input into an ideal 8-bit ADC with a voltage such that the quantization level would be 131.576839. In the absence of noise, this would quantize to level 132 for every measurement taken, thus there is nothing to be gained by averaging without noise. However, if ½ LSB of uniformly distributed noise is present in addition to the DC voltage, the converter will statistically output both 131 and 132. The histogram of these two values would favor 132 slightly since the DC voltage is slightly higher than 131.5 (the decision threshold). The expected histogram values for a varying number of samples is shown in Table 2-1.

|          | Histogram |      |               | Histogram |     |     |               |

|----------|-----------|------|---------------|-----------|-----|-----|---------------|

| Averages | 131       | 132  | Average Value | Averages  | 131 | 132 | Average Value |

| 10       | 4         | 6    | 131.6         | 2         | 1   | 1   | 131.5         |

| 100      | 42        | 58   | 131.58        | 4         | 2   | 2   | 131.5         |

| 1000     | 423       | 577  | 131.577       | 8         | 3   | 5   | 131.625       |

| 10000    | 4232      | 5768 | 131.5768      | 16        | 7   | 9   | 131.5625      |

Table 2-1 Histogram and Averaging for a Input Level of 131.576839

From the right hand side of the table, the following formula can be derived for estimating the effective number of bits with averaging  $(ENOB_A)$ :

$$ENOB_A = B + \log_2(N) \tag{2}$$

where,

B = number of converter output bits

N = number of averages

It is important to note that this relationship is only valid for a large number of averages as the noise will not be sufficiently uniform over a small number of samples. Additionally the equation is setting an upper bound on ENOB gain as a real system will not have exactly ½ LSB of uniform noise. A real system will typically have a few LSBs of Gaussian noise resulting in an ENOB gain less than that of the ideal case. A simple way to find ENOB<sub>A</sub> experimentally is to measure the SNR of a real signal with a known noise distribution and convert SNR into ENOB using equation 1.

### CHAPTER 3 DATA ACQUISITION SYSTEM DESCRIPTION

#### 3-1 System Overview

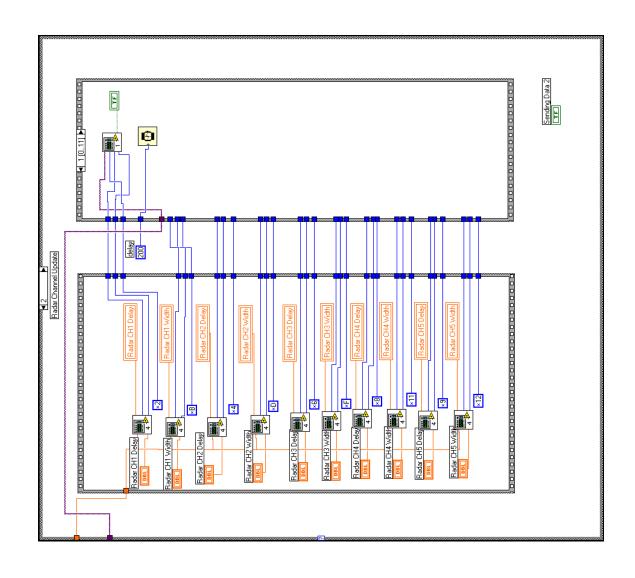

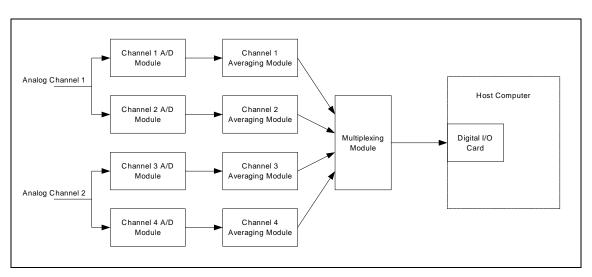

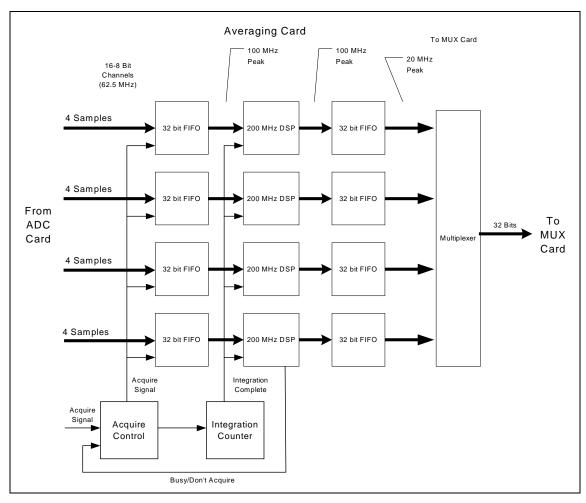

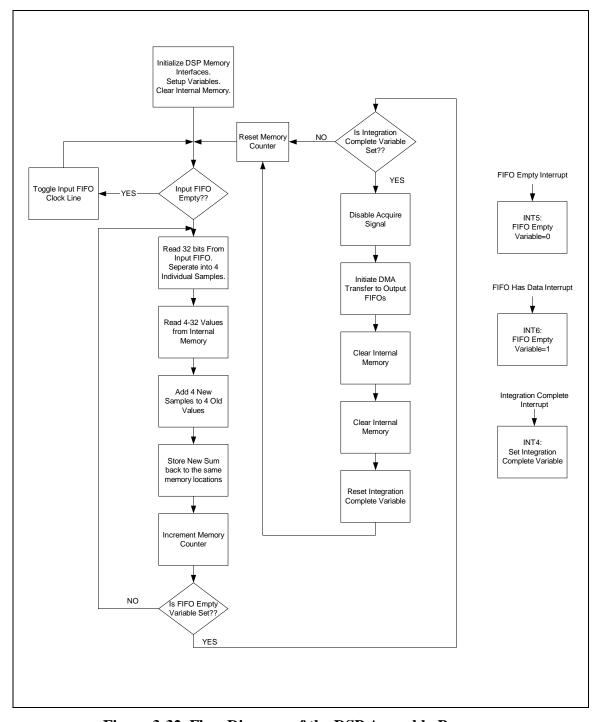

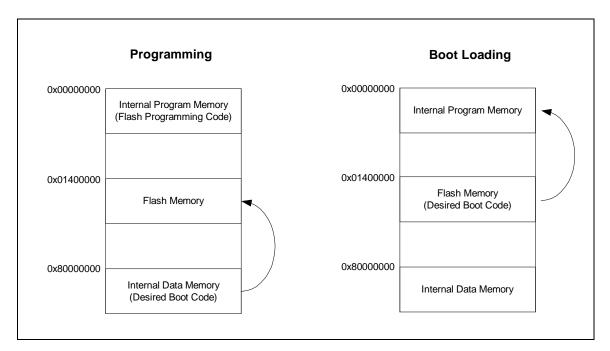

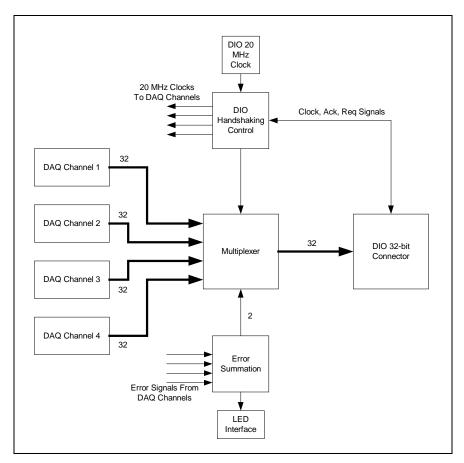

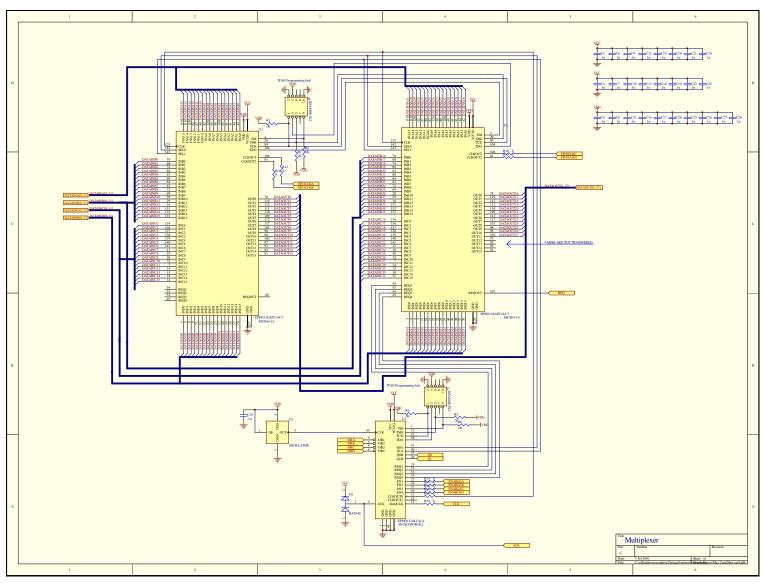

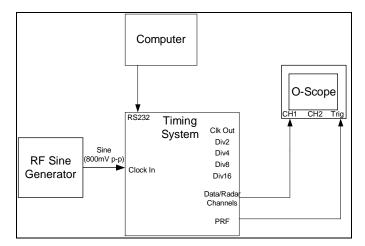

The data acquisition system consists of four modules: A/D Converter Card, Averaging Card, Multiplexer (MUX) Card, and Computer Interface Card. The configuration of these modules is shown graphically in Figure 3-1. Each A/D converter card contains a gigasample A/D integrated circuit (IC) that is the enabling technology of the entire system. Since the output signals of the converter change too rapidly for current memory/processing technologies, the A/D converter card also performs a 1:16 demultiplexing to widen the bus and slow the clock rates. The Averaging Card performs averaging on the coherent data using four digital signal processors (DSPs) and also multiplexes the data into the correct order after processing. Finally, data from the Averaging Card pass through a multiplexer card which switches access from the four acquisition channels to a single digital input/output (DIO) card on the host computer.

Figure 3-1 Overview of the Data Acquisition System

In Figure 3-1 it can be seen that the system actually consists of four separate A/D channels. Using independent analog inputs the system can be operated with 4 independent channels at 1-GSPS each. By placing a power divider at the inputs of channels 1-2 and 3-4 as shown in the figure and providing 180° clock timing to the converters a 2 channel, 2-GSPS (interleaved) system is realized. This demonstrates the easy reconfigurability which is a major advantage of a modular system.

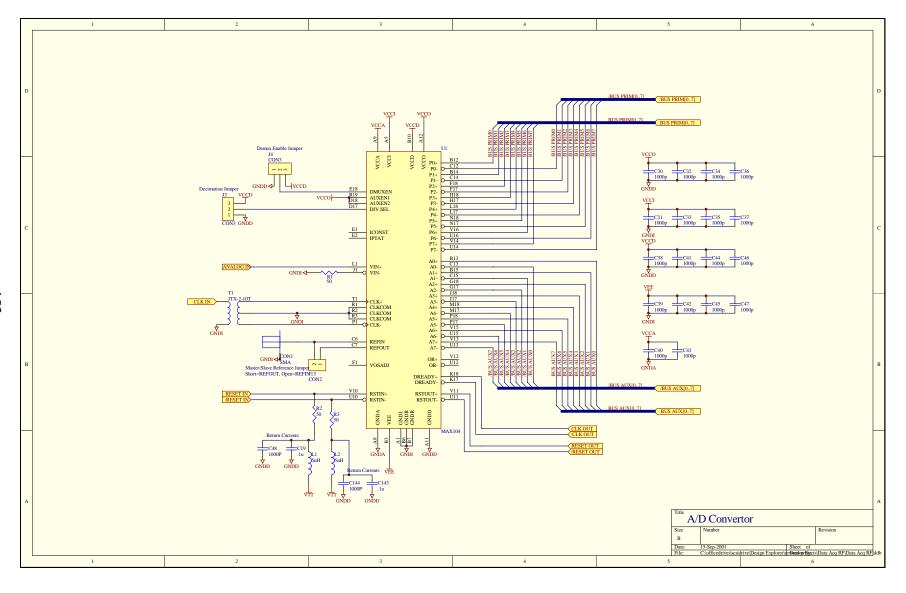

#### 3-2 Analog to Digital Converter Card

#### Overview

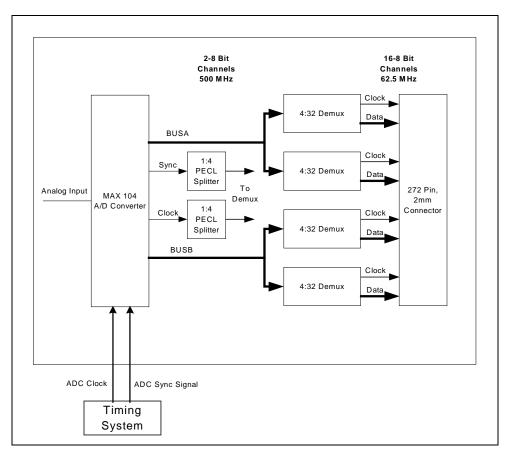

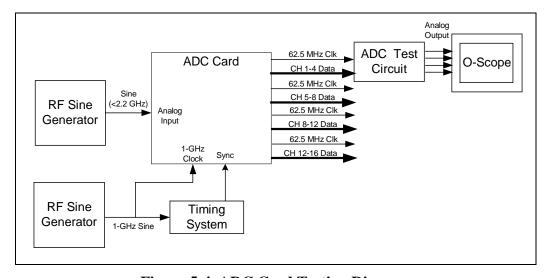

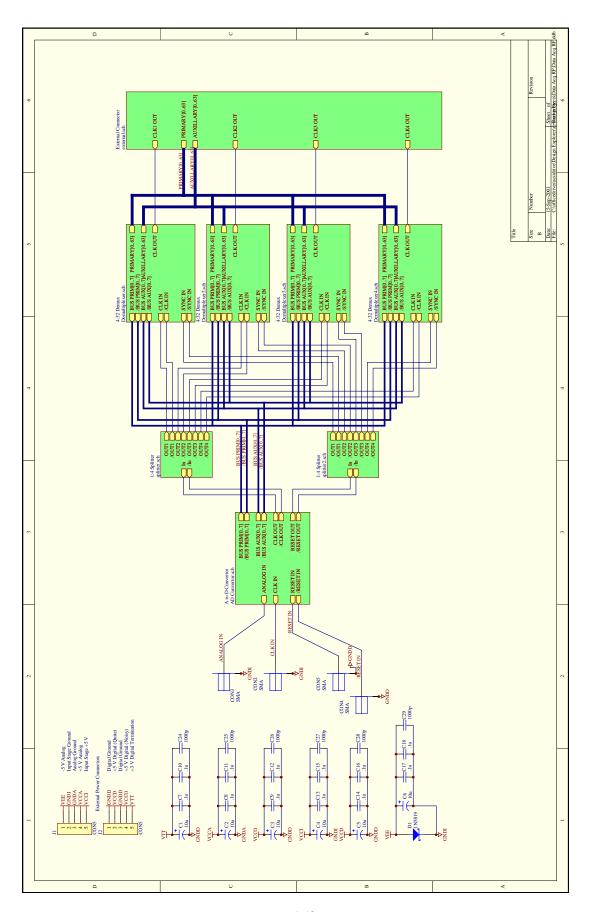

An overview of the analog to digital converter (ADC) card is shown in Figure 3-2. The 8-bit ADC is clocked using a 1-GHz sine wave from the timing system. The analog waveform is sampled upon every rising edge of this clock and the ADC divides the clock and bus frequency by two using a built in 1:2 demultiplexer. The 16-bit output from the ADC changes at a 500 MHz rate and has PECL voltage levels. These high speed signals are input directly into four 4:32 demultiplexers (demuxes) synchronized as a 16:128 demux. This serves to further reduce the bus rate to 62.5 MHz where it is output through a 272 pin connector to the Averaging Card. A synchronization signal is needed from the timing system to synchronize the demux structures so that the first sample after the PRF pulse will always be present in the same demux slot. Timing on this signal is critical as it must be consistently timed with the 1-GHz sine wave. Without this signal, coherency of the system would be lost as the first sample after the PRF pulse would be in a random demux channel.

Figure 3-2 A/D Converter Card Overview

# Detailed Description Board Physical Properties

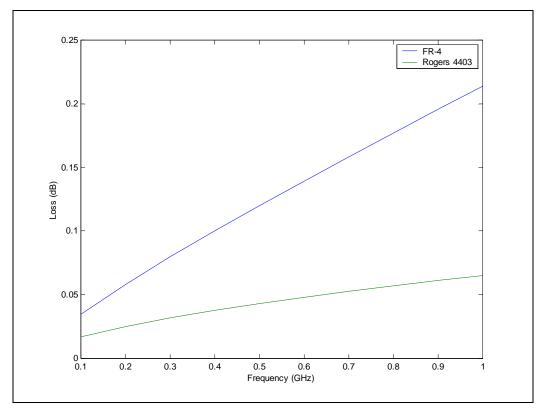

Special low loss board material is necessary for the ADC card due to the high frequencies that the analog signals may operate at (up to 2-GHz). Although the trace length is only one inch, the attenuation due to dielectric losses increases with frequency. For precise measurement of wideband signals this loss must either be minimized or compensated for digitally (in post processing). A comparison of board loss vs. frequency for a 50  $\Omega$  microstrip line (8 mil dielectric thickness) for two board materials is shown in Figure 3-3. As seen in the figure, the loss from one inch of standard FR-4 would vary from 0.05 dB to over 0.2 dB in the frequencies of interest where 0.2 dB represents about 2 least significant bits (LSBs) of the ADC with a full scale input voltage. For the same

configuration, the Rogers 4403 varies from 0.02 to 0.065 over the same range. This represents less than one LSB of error and can therefore be neglected. Additionally, if the ADCs were ever used up to the full 2.2-GHz input bandwidth, the loss difference between the two materials would become even more prominent.

Figure 3-3 Tangential Loss vs. Frequency for a One Inch Trace

An additional advantage of using low loss (RF) material is the ability to control line impedances more closely. When line impedances are closer to the ideal value, standing waves are reduced resulting in more accurate analog measurements over a wide frequency band. For digital signals, the tighter tolerance line impedance results in smaller reflections, lowering the probability of a bit error or false trigger.

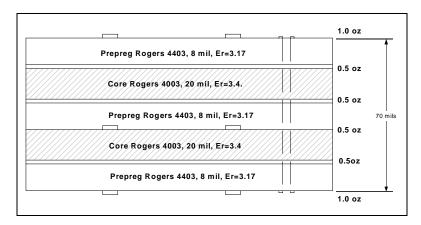

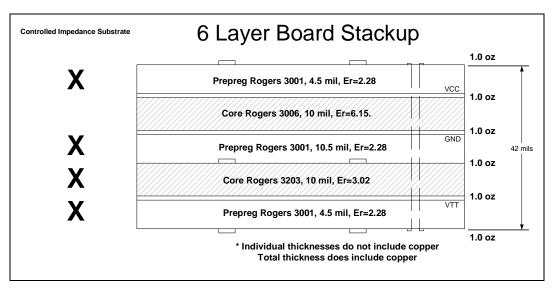

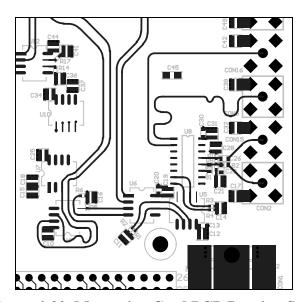

A stackup of the circuit board is shown in Figure 3-4. The internal planes are not dedicated to any particular power supply and are highly segmented due to the multiple

power sources of the mixed signal IC as seen in the board layout of APPENDIX F. The general layout of the board is modeled after the manufacturers recommended layout used in the evaluation board of the MAX104 ADC [6].

Figure 3-4 ADC Circuit Board Stackup

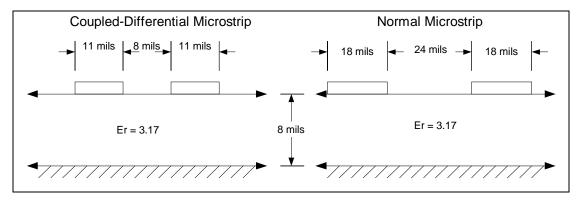

Since the logic levels of the ADC outputs are all differential PECL, a special coupled microstrip transmission line structure was used to reduce board space. The rule of thumb for digital transmission lines is to allow a spacing greater than three times the height of the dielectric [7]. For the board stackup of Figure 3-4, the line spacing would therefore be 24 mils. The 50  $\Omega$  line width is 18 mils resulting in a minimum width of 60 mils for two microstrip traces side by side. By taking advantage of the differential signaling, a coupled transmission line structure was used which acts as an RF coupler in the odd mode. The 50  $\Omega$  dimensions for this were found using the Linecalc [8] software tool and were determined to be 11 mil line widths with an 8 mil gap thereby using half the board area of regular microstrip. Since this board operates at such high frequencies, the PCB manufacturers undercut factor of 1.25 mils was added onto all high speed lines to make them as close the ideal value as possible after processing. A drawing of the two

high-speed microstrip configurations (target values after processing) is shown in Figure 3-5.

Figure 3-5 Microstrip Structures Used on High Speed Lines

For low speed (62-MHz) TTL signals the main goal was to minimize the board area while maintaining some impedance control. To minimize board area the manufacturer's minimum standard line width of 8 mils was selected (6.75 mils finished width). This results in an impedance of about 80  $\Omega$  for the microstrip and about 60  $\Omega$  for the offset stripline on layer 4. Although there is a slight impedance mismatch between these lines, Advanced Design System (ADS) simulations (and later prototype verification) showed that this was insignificant when the lines were properly terminated.

#### Circuit Design

Analysis of the circuit design should begin with the MAX104 ADC shown in Figure 3-6. A 1-GHz sine wave clock signal is input into transformer T1 which has a center tapped output to produce  $0^{\circ}$  and  $180^{\circ}$  (-3 dB) replicas of the GHz clock. These differential sine waves then drive the differential clock inputs on the MAX104. The MAX104 has internal 50  $\Omega$  laser trimmed termination resistors on the analog and clock inputs, eliminating the need for external terminations. On the rising edge of the true

clock input, the ADC's on board 2.2-GHz track and hold (T/H) amplifier latches the voltage at the analog input and the internal flash converter digitizes that value.

Figure 3-6 Schematic Layout of the MAX104 ADC

The acquired sample is output from the MAX104 via complementary PECL signaling that can operate at speeds equal to the input clock frequency. However, to simplify integration into surrounding circuitry the chip includes an on-board 1:2 demultiplexer to widen the output bus and slow the output bus speed from 1 GHz to 500 MHz. These outputs are shown in Figure 3-6 as buses P[0:7] (primary) and A[0:7] (auxiliary). Jumper J4 was added so the output multiplexer could be enabled or disabled. This was intended for debugging purposes as the downstream hardware is not capable of operating above 625 MHz.

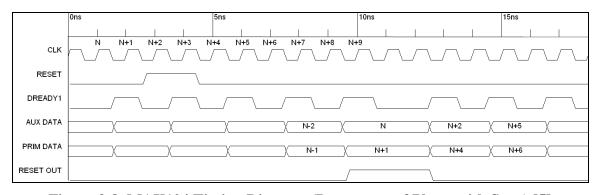

When the demultiplexer is enabled there are two output paths that a particular sample may take. This would result in a potential loss of coherency in the radar because the same sample must be output in exactly the same path after each PRF pulse. This is complicated further because the ADC uses a pipelined architecture where the data are delayed by 6-8 clock cycles from acquisition to output. To resolve this issue, the MAX104 has a synchronization input (reset) that is used to eliminate this ambiguity. By asserting a copy of the PRF pulse onto this synchronization input, the same samples are guaranteed to be on the same ADC output ports 12 clock cycles after the sync pulse is sampled high. Because there are two possibilities for the arrival of the sync pulse (demux in phase and demux out of phase) there are two possible timing diagrams shown in Figure 3-7 and Figure 3-8.

Figure 3-7 MAX104 Timing Diagram (Demux in Phase with Sync) [5]

Figure 3-8 MAX104 Timing Diagram (Demux out of Phase with Sync) [5]

For the case where *RESET* and *DREADY* are both sampled high, the output is considered in phase and no change in the flow of data is observed. For the case where *DREADY* is sampled low and *RESET* is sampled high, the immediate samples from the demux are considered out of phase. This is corrected with the converter skipping one clock cycle and losing one sample. As seen in the figures, the ADC will guarantee that the same samples (N+5 and N+6) are in the primary and secondary ports 12 clock cycles after *RESET* is sampled high. It is this synchronization feature of the demultiplexer that enables the system to maintain coherency. Note that using this type of synchronization places requirements on the timing system to consistently meet the setup and hold times of the *RESET* signal with respect to the 1-GHz sample clock.

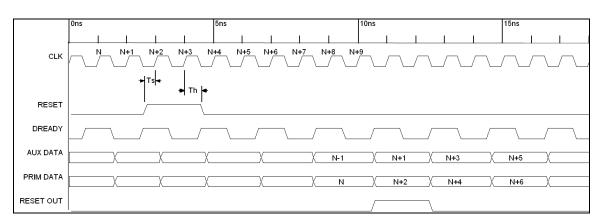

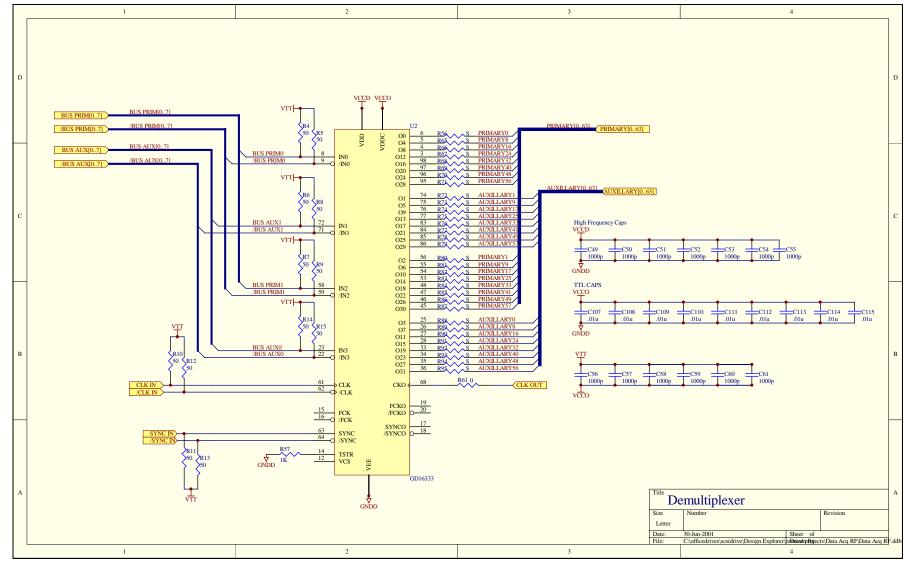

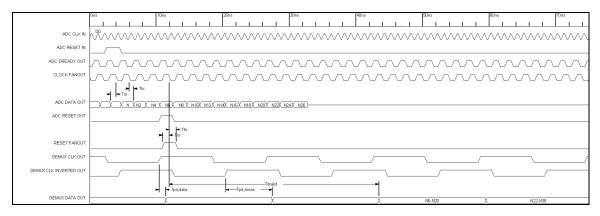

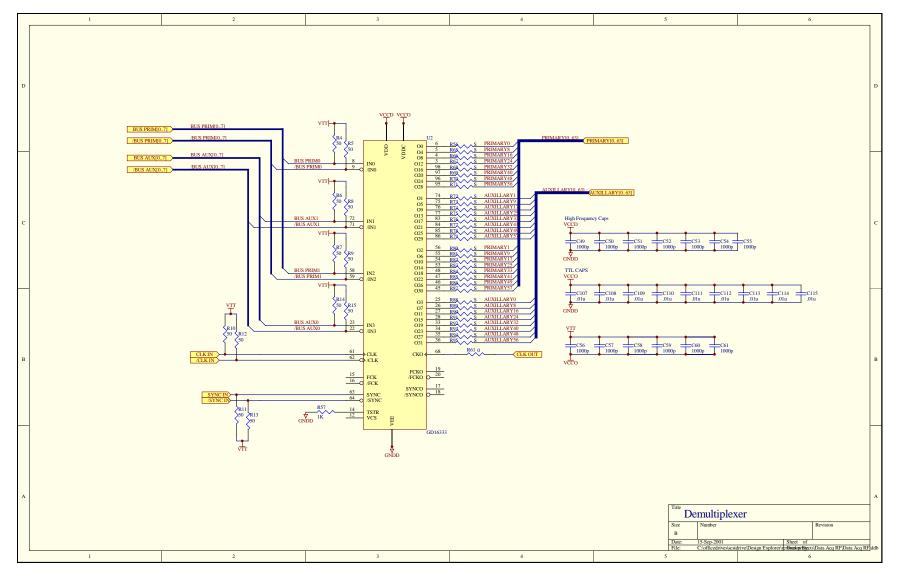

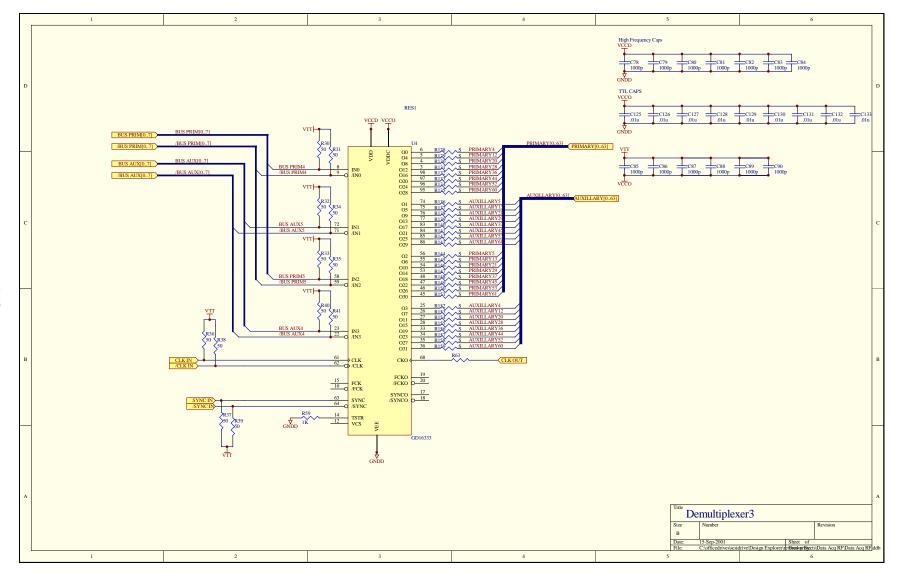

The 2:1 demultiplexed output from the MAX104 is then output into four GD16333 4:32 demultiplexers as shown in Figure 3-2. This results in an overall demultiplexing ratio of 1:16, reducing the clock rate from 1 GHz to 62.5 MHz while increasing the bus width from 8 bits to 128 bits. Since additional demultiplexers are used, the synchronization output from the MAX104 is repeated to each of the demultiplexers to maintain coherency as described above. A 1:4 PECL fanout buffer is used to fan the clock and sync signals from the MAX104 to the GD16333s. Figure 3-9 shows the schematic layout of one GD16333. As seen in the layout, all input signals are differential PECL pairs terminated through a high quality 50  $\Omega$  resistors to +3.0 V. The GD16333 inputs the 500-MHz clock and outputs a 62.5-MHz clock that is routed directly to the output connector for use by the Averaging Card. Note that each GD16333 demultiplexes signals from the ADC primary and auxiliary ports. This is because routing of the 500-MHz signals was given priority over the natural logic flow. A timing diagram

of the entire demultiplexing structure is shown in Figure 3-10 (note the GD16333 is a negative edge triggered device).

As seen in the figure, the setup and hold times of the GD16333 inputs are easily met due to the additional 500 ps propagation delay of the fanout buffers. The parameter,  $T_{pd,data}$ , in the figure is rated in the manufacturer's datasheet to be 3.2 ns. After board construction, this was measured on four chips to be about 1 ns (as shown in the figure) resulting in hold time violations on the output bus. To solve this, inverters were added on the clock output of each GD16333 resulting in the parameter  $T_{pd,meas}$  which places the rising clock edge nearly in the center of the eye. Also from the figure, it can be seen that the overall delay from the sync pulse to valid (coherent) output is 41 ns. This places a constraint on the timing system that acquisition cannot begin for at least 41 ns after the ADC sync pulse occurs. For added margin, it is recommended to delay acquisition for at least 60 ns.

Figure 3-9 GD16333 Demultiplexer Schematics

Figure 3-10 Timing Diagram of the ADC Board

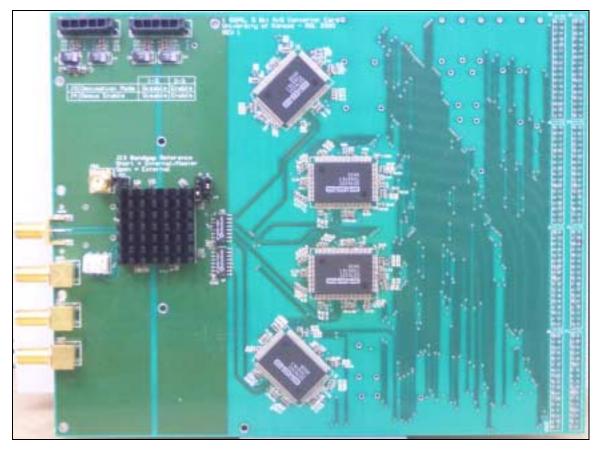

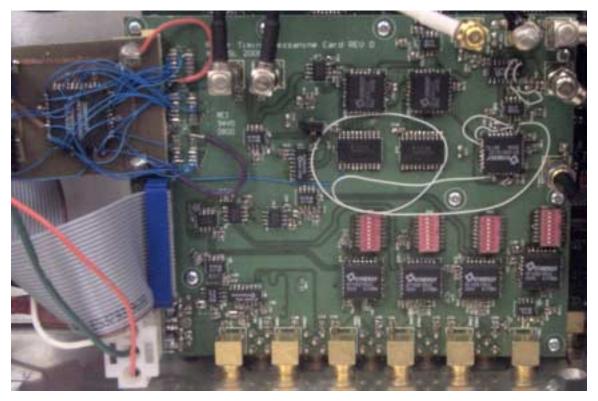

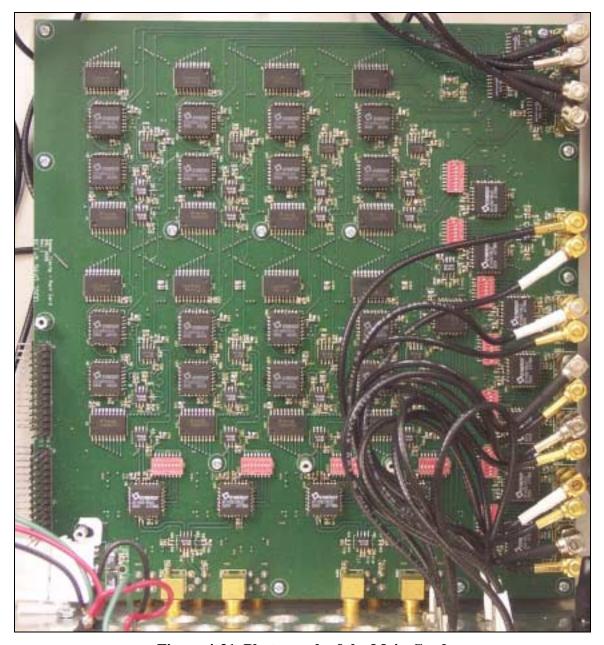

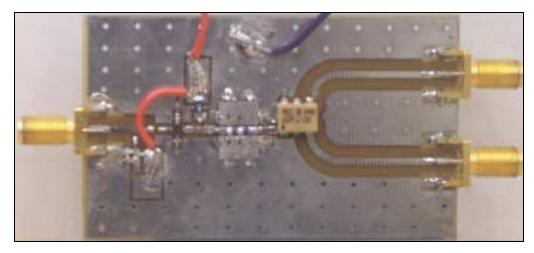

A photograph of a completed board is shown in Figure 3-11 with the complete board layout shown given in APPENDIX F. As seen in the figure, a semicircular layout was used for optimum signal integrity and equal propagation delay to each demultiplexer. Because the board layout and schematics are both designed around this one goal, the low speed (62.5-MHz) data are fragmented with two bits from each of the output bytes going to each demultiplexer. To defragment the low speed data before exiting through the card connector approximately 25% of the board area was needed to route the lines from a seemingly "random" to an orderly pattern.

Figure 3-11 Photograph of a Completed ADC Card

#### Revision History/Future

This board has been revised once for a board material change. The original board material selected was the Roger 3000 series. The timing Mezzanine Card was manufactured using this material and the physical properties were found to be highly undesirable for multilayered boards. The 3000 series material is soft and pliable resulting in excessive warpage around drill holes. The 4000 series material is very similar to standard FR-4 except that it has low loss and a controlled dielectric constant making it ideal for multilayered high frequency boards.

The goal of the original design was to have the data output through the connector in chronological order with the  $1^{st}$  sample at the top and the  $16^{th}$  sample at the bottom of

the card. However, when testing the Averaging Card it was discovered that this ideal pattern was not realized due to an oversight in the design. This was easily corrected with a firmware change by re-ordering the data in the Averaging Card multiplexer. A comparison of the two patterns is shown in Table 3-1. In the future, if a completely new system is designed using similar technology, this should be corrected to simplify signal flow in the downstream hardware.

| Desired Order |              |          |           |           |           |           |           |           |     |

|---------------|--------------|----------|-----------|-----------|-----------|-----------|-----------|-----------|-----|

|               | Sample 3     | Sample 4 | Sample 7  | Sample 8  | Sample 11 | Sample 12 | Sample 15 | Sample 16 | 272 |

| 1             | Sample 1     | Sample 2 | Sample 5  | Sample 6  | Sample 9  | Sample 10 | Sample 13 | Sample 14 |     |

|               | Actual Order |          |           |           |           |           |           |           |     |

|               | Sample 6     | Sample 8 | Sample 14 | Sample 16 | Sample 5  | Sample 7  | Sample 13 | Sample 15 | 272 |

| 1             | Sample 2     | Sample 4 | Sample 10 | Sample 12 | Sample 1  | Sample 3  | Sample 9  | Sample 11 |     |

Table 3-1 Comparison of Intended and Actual Output Connector Pinout

#### 3-3 Averaging Card

#### Overview

The averaging card provides a link between the ADC and computer. In addition to a physical link, it must perform the following functions:

- Perform coherent averaging on the acquired data.

- Gate the output from the ADC card so only the desired number of samples are acquired.

- Provide buffering between the computer DIO card and the ADC.

- Multiplex the 16-ADC output busses into a single bus for the computer DIO card link.

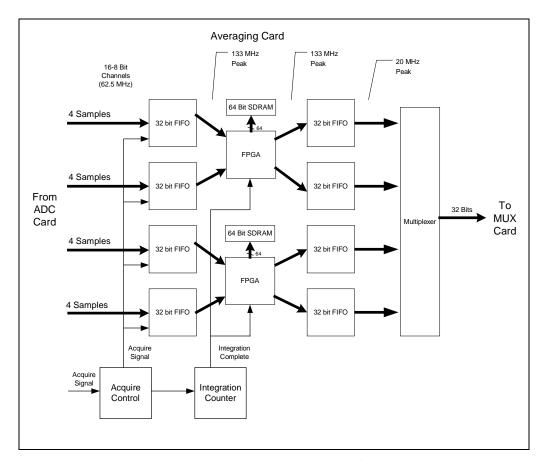

An overview of the averaging card is shown in Figure 3-12.

Figure 3-12 Averaging Card Overview

As seen in the figure, the 200-MHz DSPs are the focal point of the entire card. The DSPs perform coherent averaging by adding incoming samples to the previous samples stored in internal memory. Using the DSP's internal memory results in a cleaner PCB layout as no external memory chips are required. It also simplifies the design since a signal level timing analysis is not required for the internal memory interface. After the DSP has completed the required number of averages, the processed data are transferred to the output FIFOs where they are stored until the computer DIO card is ready for transfer.

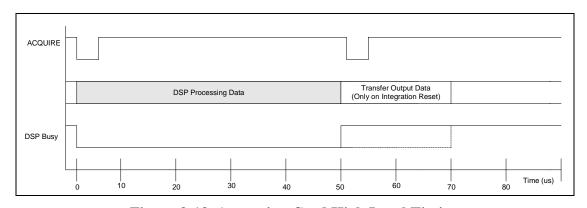

A high level timing analysis for the entire board is shown in Figure 3-13. As seen in the figure, the maximum PRF of the radar can be limited by the DSPs processing rate.

The averaging card does not input a raw PRF signal, the input must be a PRF pulse with a delay and width equal to the desired sampling window. This is represented in the figure as the *Acquire* signal. For example, with a sampling interval of 1 ns, if the user wishes to acquire 8,000 samples the *Acquire* signal must have a pulse width of 8,000 ns. Figure 3-13 shows the processing time goal of the actual system for an 8,000-sample acquisition window. As seen in the figure, the processing time was estimated to be approximately 45  $\mu$ s, which limits the PRI to around 50  $\mu$ s (PRF = 20 kHz). This processing time could be reduced by upgrading the DSPs to operate at a higher frequency. If 300-MHz DSPs were used, the estimated maximum PRF would increase to approximately 30 kHz for an 8,000-sample acquisition window.

Figure 3-13 Averaging Card High Level Timing

When averaging is complete, the DSPs take approximately 20 µs to transfer the data to the output buffers and clear internal memory to start a new averaging cycle. During this time, if the *ACQUIRE* signal becomes low, it is ignored until the output transfer is complete. By implementing this "acquire blocking" feature, the PRF can be increased until it is limited only by processing time and not by the output FIFO transfer time that only occurs every 100-1000 acquisition cycles (the number of coherent

averages). If the transfer completes while the *ACQUIRE* signal is still low, the system will not acquire a partial interval as the acquire circuitry is edge triggered.

### **Detailed Description**

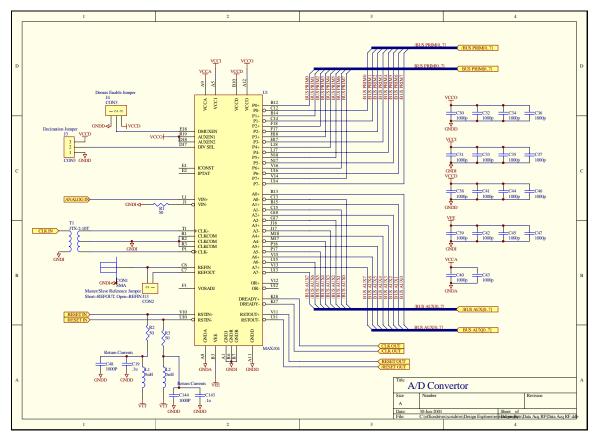

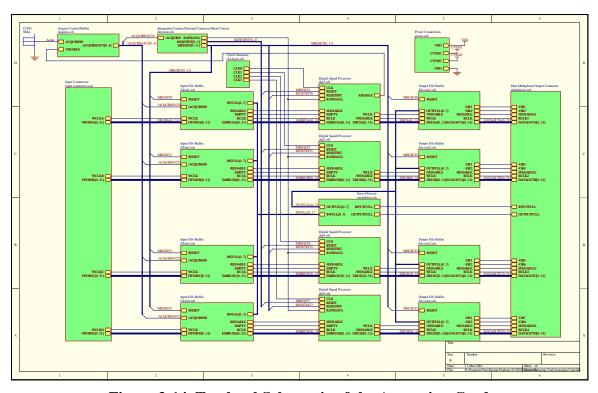

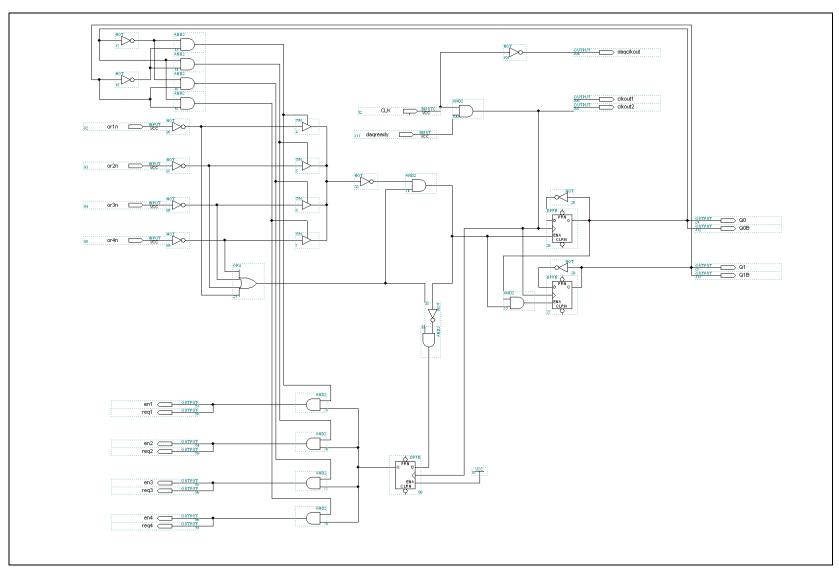

A detailed discussion of the Averaging Card should begin with the top level of the schematics shown in Figure 3-14. The complete schematics are shown in 0. Initially, all FIFOs are empty and the signal processors are idle, waiting to process data. Data are input from the ADC card through a 272-pin, 2-mm connector and are presented to the input FIFOs of the four averaging card channels. Each channel receives it's own clock from the ADC card and the data and clocks are always present (they are not gated in any way). To capture data from the stream, an *ACQUIRE* signal is asserted at connector *CON1* which is input into the acquire control circuitry. The acquire control circuitry then activates the input FIFOs which capture the data.

Figure 3-14 Top level Schematic of the Averaging Card

As data are input into the FIFOs, the FIFO empty flags will toggle from high to low. This triggers an interrupt in the associated DSP which then executes code to read and processed data from the FIFO. After each new sample is read, an internal count is incremented so that samples will be stored in consecutive locations in the processors internal memory. After the desired number of samples have been acquired, the *ACQUIRE* signal is de-asserted which inhibits the input FIFOs from storing new data. With no input data, the FIFO will eventually become empty as the DSP continues to read. The FIFO empty flag then triggers an interrupt in the DSP causing the DSP to cease reading new data and go into an idle state until another acquisition cycle begins.

An average counter operates in parallel to the FIFOs and DSPs. This counter is incremented for each acquisition period and counts the number of coherent integrations that have occurred. When the desired number of integrations is complete, the counter toggles the *resetint* lines to tell each DSP that, at the end of the current processing period, the data must be flushed to begin a new averaging sequence. When the input FIFOs become empty, instead of immediately going to an idle state, the processors will output the averaged data from internal memory to the output FIFOs where the data are stored until the downstream hardware is ready for transfer to the computer. As data are transferred to the output FIFOs, the FIFO empty flags are de-asserted signaling the downstream hardware that the Averaging Card has data to transfer. After all data are transferred to the output FIFOs, the DSPs clear their internal memory and go to an idle state to wait for a new acquisition period.

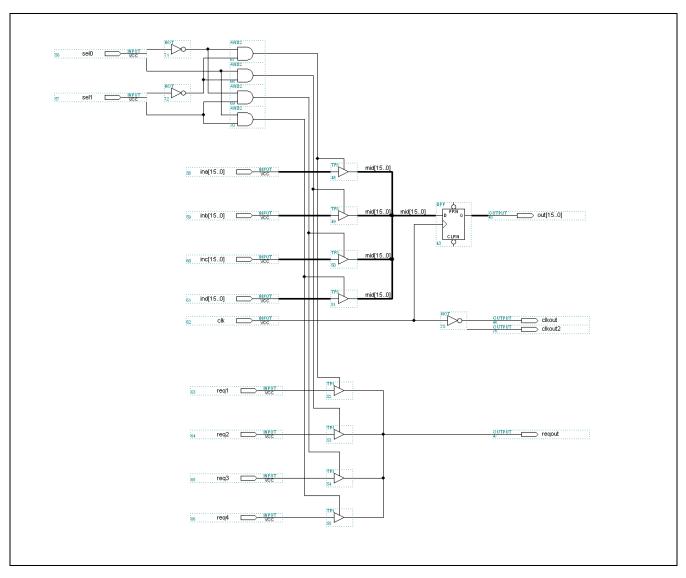

When the computer DIO card is ready to input data, a control line on the Averaging Card output multiplexer is toggled by the downstream hardware. The output

multiplexer will then begin transferring data from the output FIFOs to the 60 pin output connector. An additional (non obvious) function of the multiplexer is to resequence the four processing channels to the correct temporal order to ease post-processing requirements and reduce processing time for real time display on the computer monitor.

The remainder of this section will discuss the circuitry of each of the hierarchical blocks in detail.

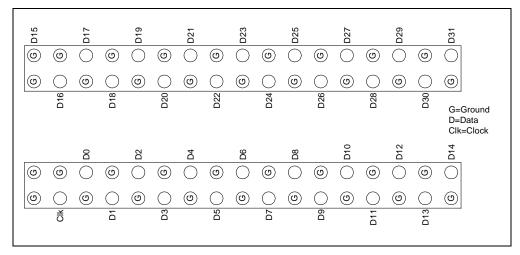

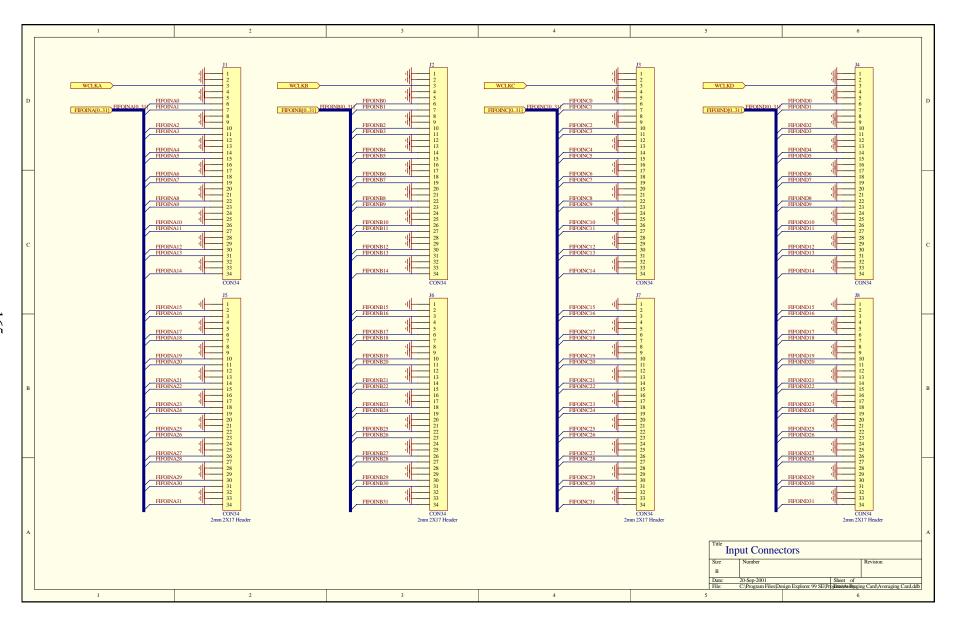

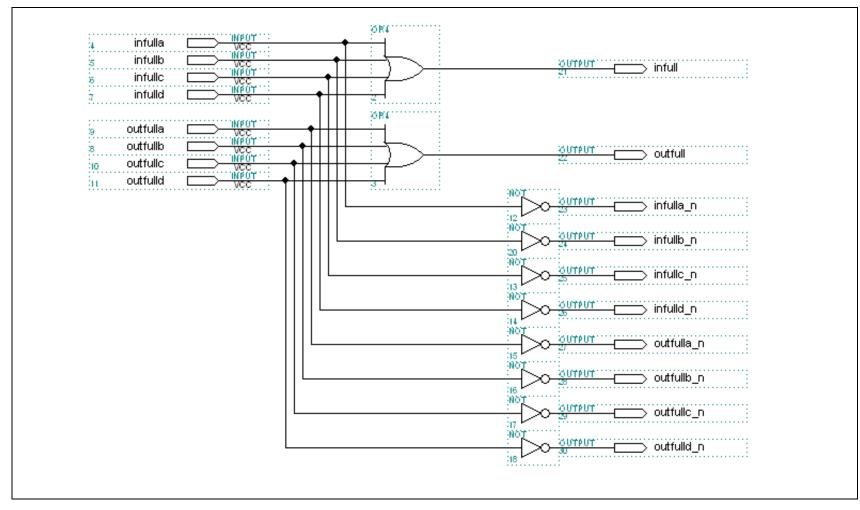

### **Input Connector**

The purpose of the input connector is to provide a mechanical and electrical connection between the Averaging Card and ADC card with minimal disturbance to the integrity of the high-speed digital signals. The input bus is 128 bits wide with four clock signals for a total of 132 signals that must be transmitted between the two boards. The design constraint was to allow these signals to operate at 125 MHz to support a doubling of the current 62.5-MHz rate. At these speeds signal integrity is a prime concern so a 1:1 ratio of grounds and signals was desired requiring approximately 264 total connections. Based on connector availability, cost, and physical constraints, a double row of standard 2 mm connectors was selected. A photograph of the connectors with the signal-ground pattern is shown in Figure 3-15.

Figure 3-15 Input Connector and Pinout Pattern

The pinout of Figure 3-15 was selected for it's effective use of ground signals to reduce the possibility of crosstalk and provide a low inductance path for return currents. As seen in the figure, three ground pins surround every signal and no two signal pins are adjacent to each other. The impedance of this configuration was approximated by treating the pins as parallel wires [10]. Since the exact electrical properties of the connector's dielectric were unknown the impedance was calculated with a dielectric constant varying from 2 to 5. Using this approximation, the impedance was estimated to be around 40-60  $\Omega$ . The entire transmission line structure was simulated in EESOF as shown in the Input FIFO section below. The simulation shows that since the length of the connector is only 200 mils, the impedance can vary drastically with little effect on signal integrity and therefore a more precise impedance analysis is not necessary.

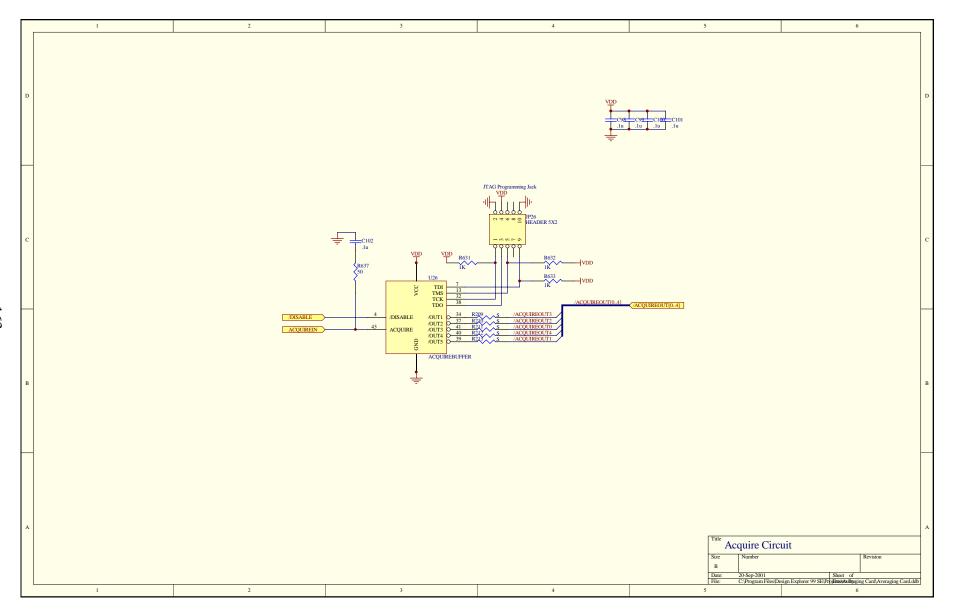

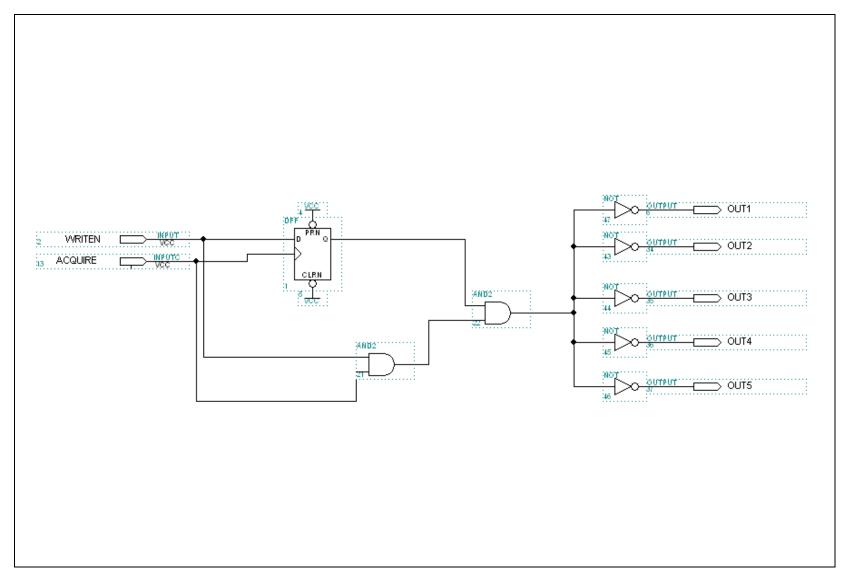

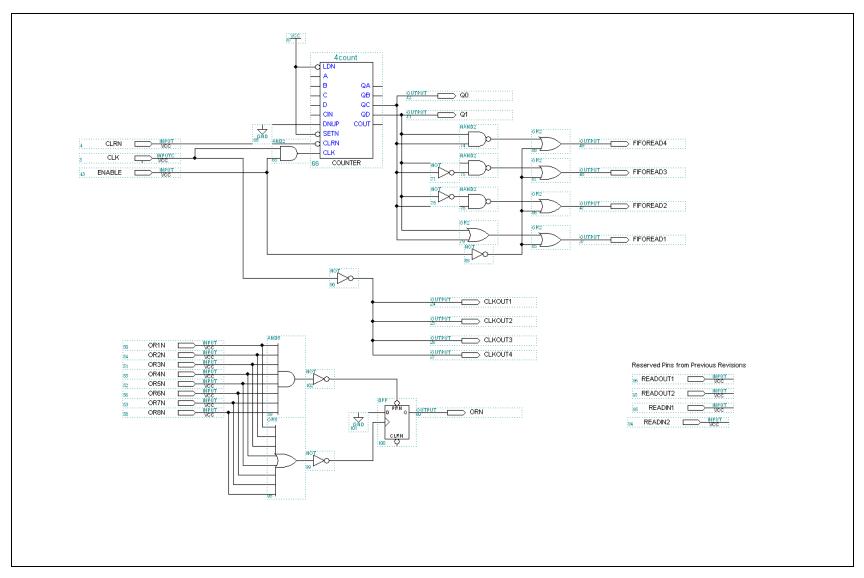

### **Acquire Controller**

The purpose of the acquire controller is to fan out four copies of the acquire signal and to allow disabling of the acquire signal when the DSPs are transferring data to the output FIFOs. This function was implemented in a single Altera PLD. The PLD

program schematic is shown in APPENDIX K. A timing analysis of the program is shown in Figure 3-16.

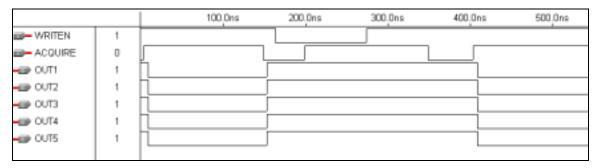

Figure 3-16 Acquire Control Timing Diagram

As seen in the timing diagram, when the *WRITEN* signal is high, the acquire signal simply passes through the device to the five outputs. When the DSPs are busy transferring data to the output FIFOs, they will pull the *WRITEN* signal low and any *ACQUIRE* signals will be ignored. After the DSPs are ready for more data, the *WRITEN* signal goes high and acquisition continues. Note again that the blocking is edge sensitive so that if the *WRITEN* signal is released while *ACQUIRE* is still high (275 ns in the figure), the output does not change until the next *ACQUIRE* rising edge (400 ns in the figure).

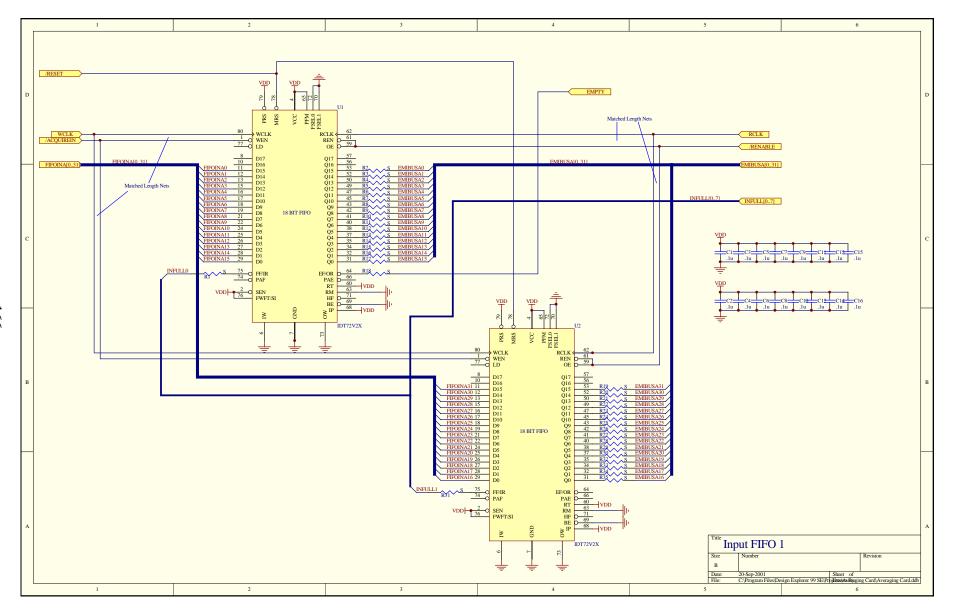

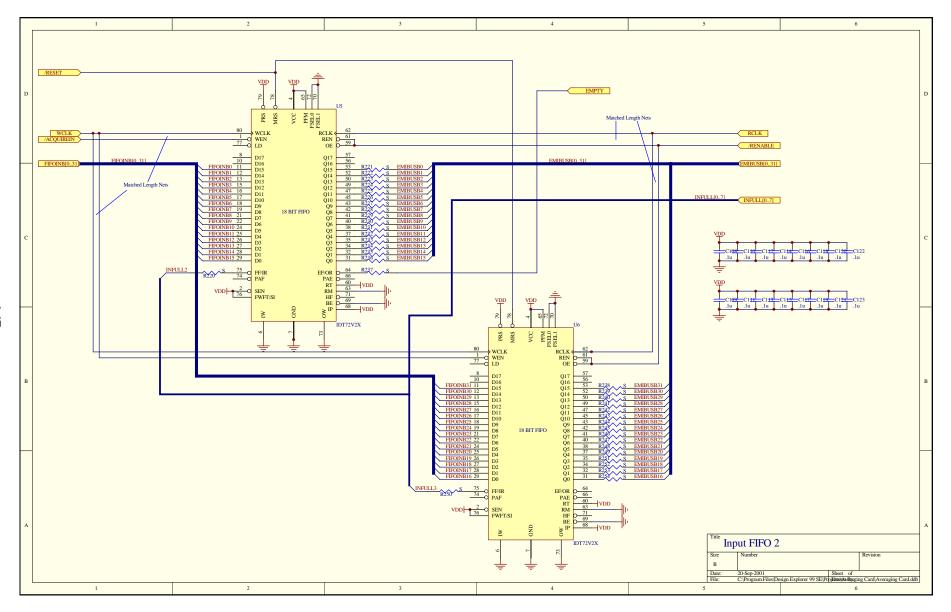

### **Input FIFOs**

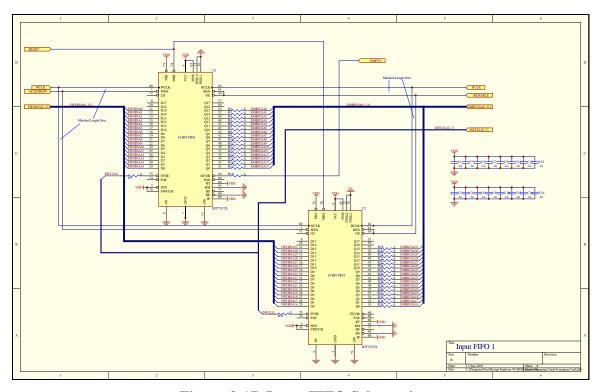

The input FIFO structure is shown in Figure 3-17. A 32 bit FIFO was needed for each of the four DSP channels, however, due to availability constraints two 18 bit FIFOs were paired to construct a 36 bit FIFO with four unused bits. The circuit operates as described previously with the data and clock always present on the input. When the acquire signal is asserted, the write enable is asserted on the FIFO input causing it to capture the input data. After three output clock cycles [9], the output ready (*OR*) flag toggles low signifying that the FIFO has data on the output ready to be transferred. This

operating mode is called first word fall through (FWFT) [9] and it allows instant access to the first word when the DSP is ready to read. The DSP will then assert the *RENABLE* signal causing the first word to output immediately and the FIFO will increment it's memory pointer to the next location in sequence. When the FIFO becomes empty, the *OR* flag toggles high and further output accesses will return the same (final) value.

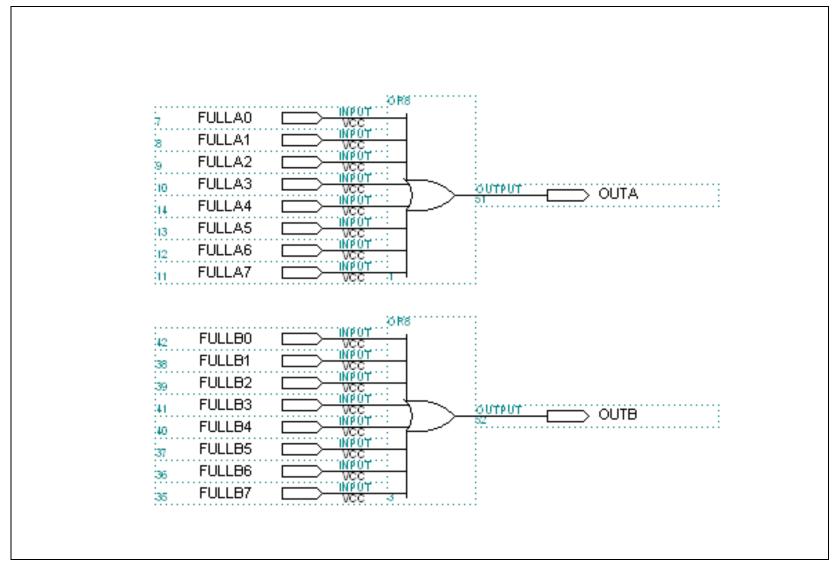

Figure 3-17 Input FIFO Schematic

The disadvantages of this "dual FIFO" method are increased PCB area and additional loading on the clock and enable signals which must drive two devices in parallel instead of a single 36-bit device. The increased board space was not a significant problem in this design as the only size constraint was the manufacturability of the PCB. However, signal integrity of the clock and enable lines was a concern since the FIFOs were designed to operate at 125 MHz. A split (matched length) transmission line

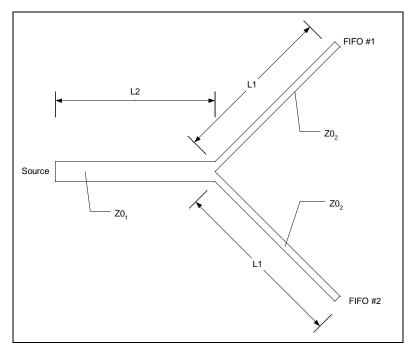

structure was incorporated to minimize reflections and avoid daisy chaining on the series terminated lines. This special structure is shown graphically in Figure 3-18.

Figure 3-18 Split Transmission Line Structure for Dual FIFOs

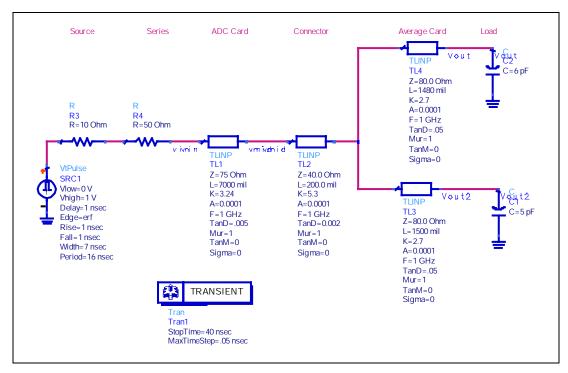

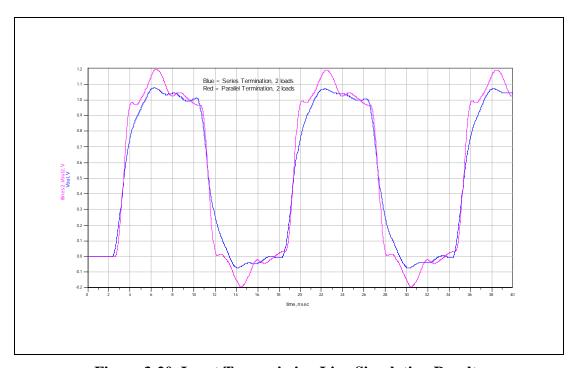

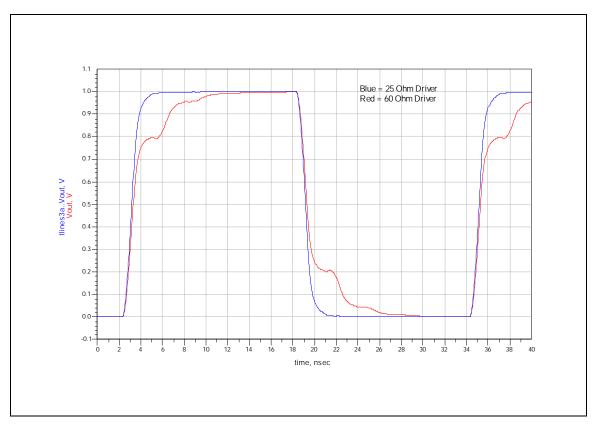

For the structure shown in the figure, no reflection will occur at the junction if  $ZO_2$  is twice  $ZO_1$ . Additionally, for a source terminated line, the length, LI, of the two splits must be exactly equal to create the ideal response. In practice, line impedances on a dense board will typically range from 60 to 80  $\Omega$ . To minimize reflections the source line impedance would therefore need to be 30 to 40  $\Omega$  for a matched condition. Since the source line impedance on the ADC card is 75  $\Omega$ , a significant mismatch is generated. An EESOF simulation model of the entire structure is shown in Figure 3-19 and Figure 3-20 and the actual eye measurement at the FIFO inputs is shown in Figure 3-21. Note that the simulation includes non identical loads (representing the two FIFO inputs) and non-identical line lengths as is the case in a real PCB.

Figure 3-19 Simulation Model of Input Transmission Line Structure

Figure 3-20 Input Transmission Line Simulation Results

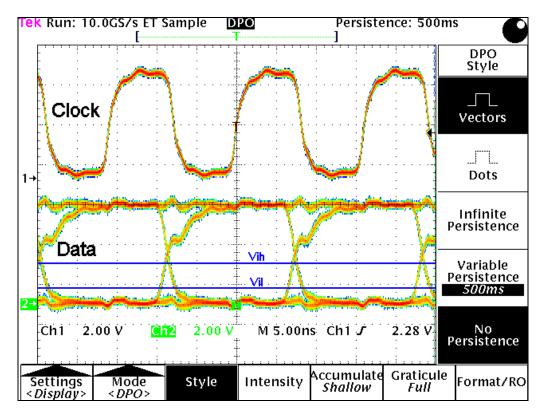

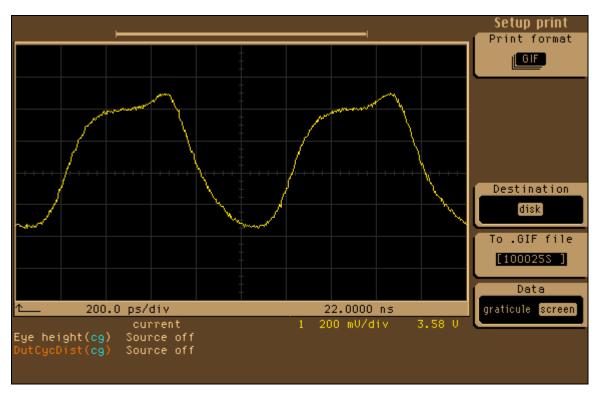

Figure 3-21 Eye Measurement at the FIFO Inputs

The simulation shows that the impedance, length, and load mismatches are acceptable since the length, LI, is relatively short (1.5 inches). The simulation also shows that the series termination method produces a similar but slightly smoother step response than a parallel termination. The series termination was selected for this reason and because a capacitively coupled or Thevenin termination is required for TTL parallel terminations. This would require two termination components for each line where the series termination method requires only one. Looking at the actual measurement results, the exact shape of the clock waveform is not identical to the simulated waveform but the smoothness and amplitude of the reflections are similar.

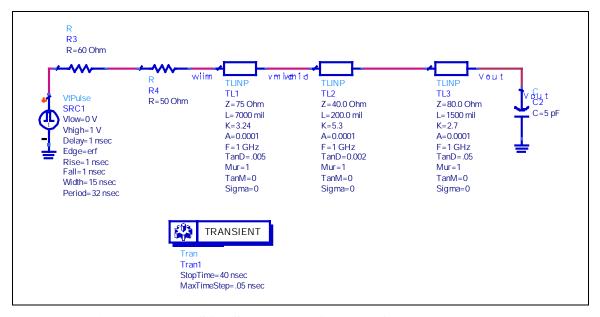

For the FIFO input data lines, the transmission line structure is more traditional with a source termination and a single load. However, viewing the waveform of Figure 3-21, the rising edge of the data signals has a significant distortion. This is due to the

differing source impedance of the data line driver for a high or low state. Again, using EESOF simulation, the line response was recreated with a source impedance of  $60 \Omega$  for a logic high and  $25 \Omega$  for a logic low. The simulation and results are shown in Figure 3-22 and Figure 3-23. The current level of distortion on the rising edge is still acceptable given the logic levels shown in the figure. If it is desired to optimize waveform distortion, a smaller value of series resistor (25-35  $\Omega$ ) could be selected to compromise between rising edge and falling edge distortion. The clock signals shown above do not exhibit this non-symmetric behavior because a separate buffer with different output characteristics was used as a source on those lines.

Figure 3-22 EESOF Simulation of the FIFO Input Data Lines

Figure 3-23 EESOF FIFO Input Data Simulation Results

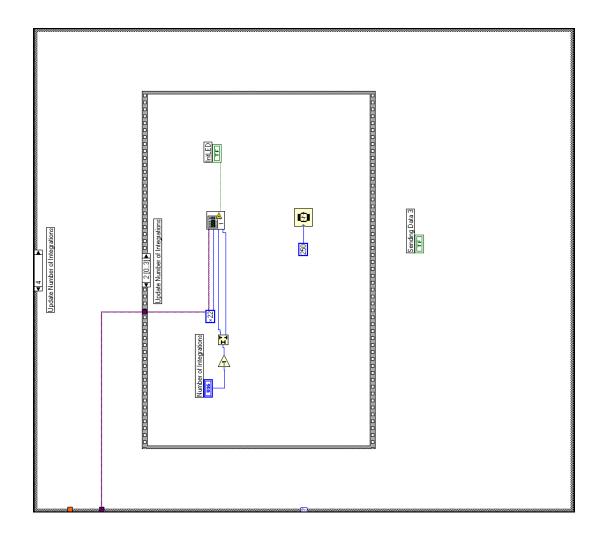

# **Integration Counter and Reset Controller**

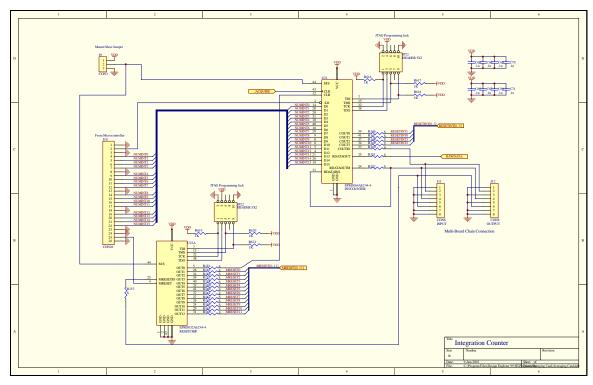

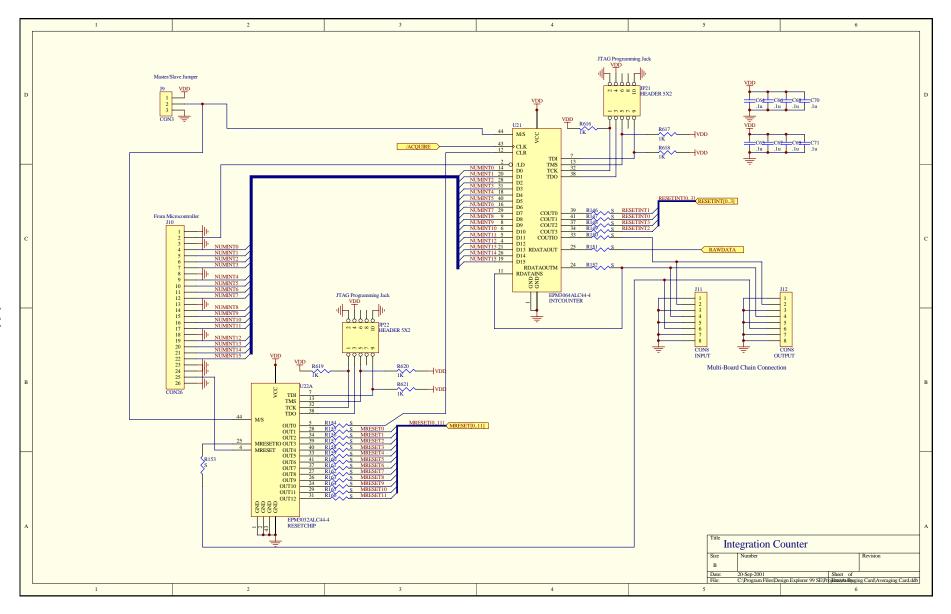

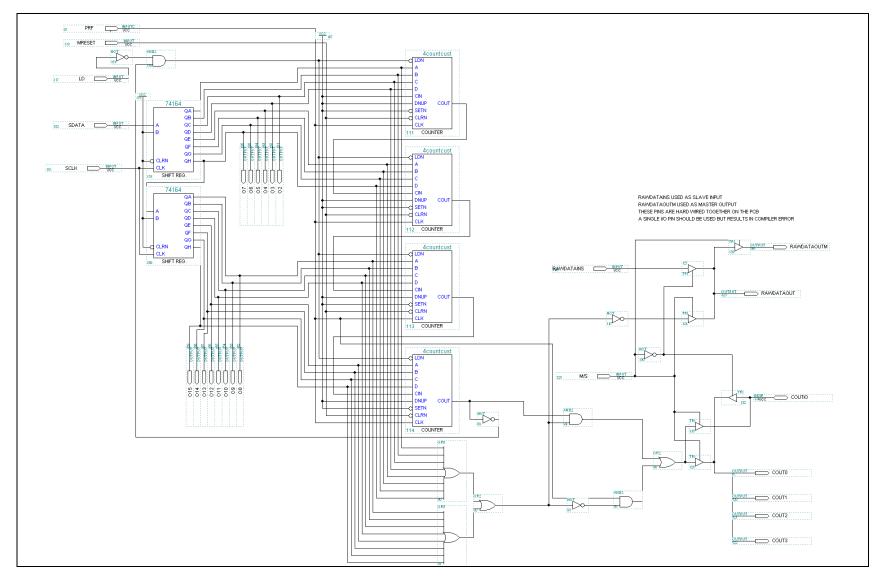

The integration counter and reset controller were both implemented using Altera PLDs. The schematic for both circuits is shown in Figure 3-24. Because the data acquisition system will have multiple averaging cards and the integration count on all cards must be synchronized, the reset and integration circuit operates in either a master or slave mode. The mode is manually selected using jumper J9.

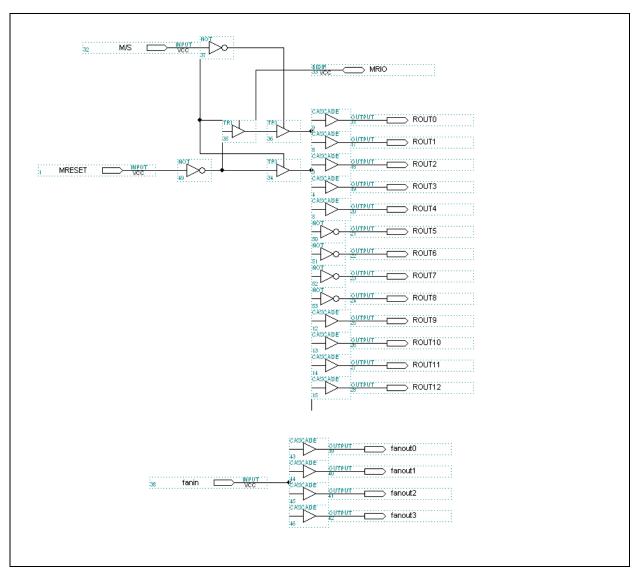

Figure 3-24 Integration Counter and Reset Schematics

# Master Averaging Card

The master Averaging Card is the only card in the system that actually counts the number of integrations. This is performed by PLD U21 by incrementing an internal counter at each rising edge of the *ACQUIRE* signal. After reset, the computer system programs the desired number of integrations into the integration counter. When the internal count is equal to the programmed value, the *RESETINT* signals are asserted to signal the DSPs that an averaging cycle is complete.

The master Averaging Card must pass the *RESETINT* signal to the slave cards in the system. This is output via pin 33 on the integration counter and transferred to the other boards via connectors J11 and J12. Two connectors are used so that multiple boards may be chained together vertically. Connector J11 is located on the top of the PCB and J12 on the bottom. When the cards are mounted horizontally and stacked

vertically in a rack, the user connects J11 of the bottom card to J12 of the top card to distribute the *RESETINT* signal through the entire stack of cards. Note, with this configuration, the master card can be placed anywhere in the stack. The master PLD output is set to a slow slew rate mode, reducing the edge rate of the PLD to over 10 ns thus making transmission line effects negligible for the chain.

The master Averaging Card is connected directly to the timing system microcontroller through connector J10. This connector contains the necessary signals to transfer the number of integrations and the reset signal from the system microcontroller to the integration counter and reset controller. The number of integrations is asserted on the 16 data lines and the load line (J10 pin 2) is asserted to latch the value into the integration counter chip. The reset signal is asserted onto the reset controller chip. In master mode, the reset controller distributes the signal with the correct polarity (active high or active low) to 13 lines on the master Averaging Card. Additionally, line 25 is used as an output and distributes the reset signal to the other Averaging Cards via connectors J11 and J12 as described previously.

Originally, the system was designed for a 16-bit latched parallel connection to transfer the integration count. In order to reduce the pin count on the microcontroller, the integration counter was later modified for a serial load connection. The serial connection remaps the data pins as shown in Table 3-2.

| Pin | Parallel Load<br>Function | Serial Load<br>Function | Pin | Parallel Load<br>Function | Serial Load<br>Function |

|-----|---------------------------|-------------------------|-----|---------------------------|-------------------------|

| 1   | GND                       | GND                     | 14  | Data8                     |                         |

| 2   | Latch                     | Latch                   | 15  | Data9                     |                         |

| 3   | GND                       | GND                     | 16  | Data10                    |                         |

| 4   | Data0                     | Ser Data                | 17  | Data11                    |                         |

| 5   | Data1                     | Ser Clock               | 18  | GND                       | GND                     |

| 6   | Data2                     |                         | 19  | Data12                    |                         |

| 7   | Data3                     |                         | 20  | Data13                    |                         |

| 8   | GND                       | GND                     | 21  | Data14                    |                         |

| 9   | Data4                     |                         | 22  | Data15                    |                         |

| 10  | Data5                     |                         | 23  | GND                       | GND                     |

| 11  | Data6                     |                         | 24  | GND                       | GND                     |

| 12  | Data7                     |                         | 25  | Reset                     | Reset                   |

| 13  | GND                       | GND                     | 26  | GND                       | GND                     |

Table 3-2 Serial and Parallel Load Pinouts of Connector J10

From the schematics, two additional signals (*RDATAINS* and *RDATAOUTM*) are shown from the integration counter to connectors J11 and J12. The *RDATAOUTM* signal is asserted by the master Averaging Card when the integration count is set to one (raw data). The RDATAINS is used by a slave card as an input for the same signal. These lines were originally intended so the DSP could execute different code to improve the throughput of raw data. This feature was never implemented in the DSPs and these lines are currently unused.

#### Slave Averaging Card

In slave mode, the reset and integration complete signals are input from connectors J11 and J12. These signals are asserted on pin 25 of the reset controller and pin 33 of the integration counter. The reset controller operates identically in master or slave mode except that in slave mode the reset input comes from the master Averaging Card instead of the microcontroller. In slave mode, the integration counter simply fans the *INTCOUNT* signal from connectors J11 and J12 to the four DSPs and does not perform any other function.

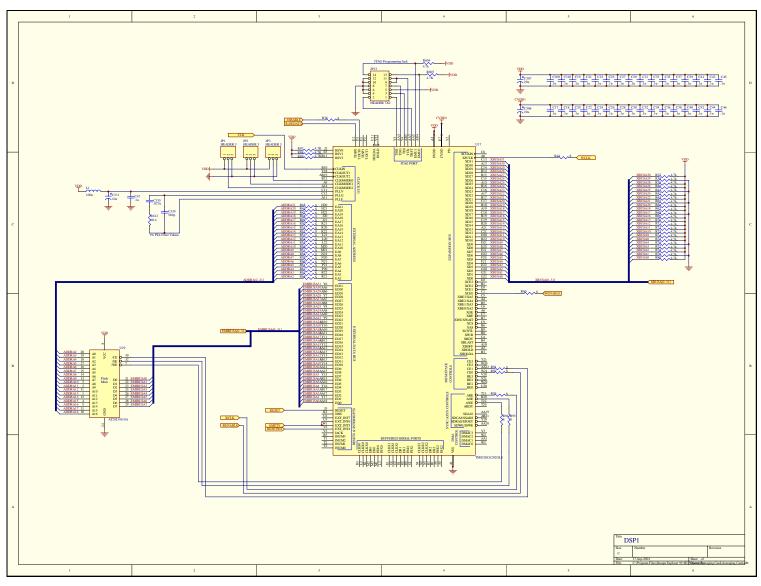

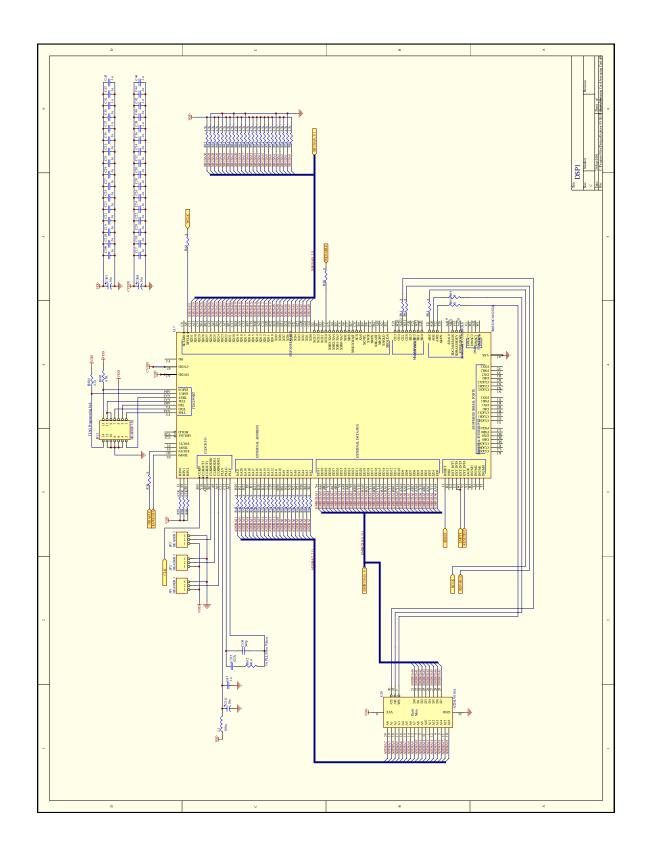

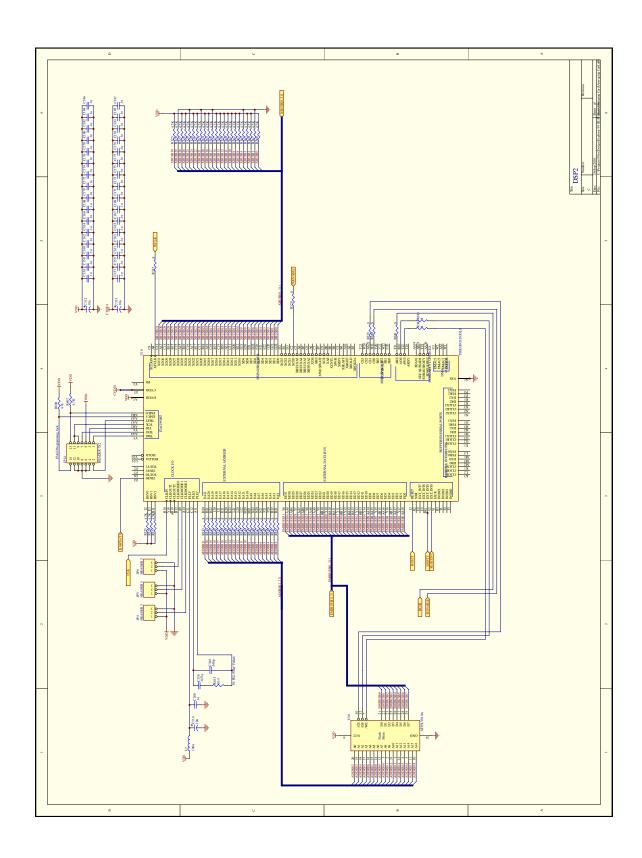

### **Digital Signal Processors**

The Texas Instruments TMS320C6202 200-MHz digital signal processors were selected for this design based on their high speed and dual 32-bit memory interface busses. The digital signal processor schematic is shown in Figure 3-25. From the figure, the two main DSP interface busses can be seen. The 32-bit external memory interface (EMIF) bus shown on the left side of the schematic is used for the input FIFOs and the flash memory used for processor boot loading. The 32-bit expansion memory interface (XMIF) bus shown on the right side of the schematic is used solely for the output FIFOs. In the lower left of the schematic are the reset, input FIFO empty, and reset integration interrupts all of which were previously described. The JTAG programming interface seen at the top of the schematic is used to interface the DSP directly to a computer for programming and debugging. A disable signal is output from the general purpose output *TOUTO*. This signal is used to disable the acquire signal when the DSP is sending data to the output FIFO.

Figure 3-25 DSP Schematic

#### EMIF Interface

The EMIF interface is a 32-bit synchronous or asynchronous bus that provides a glueless interface to a variety of standard memory types. Four separate address spaces can be accessed without glue logic and are activated using signals *CE0-CE3*. In asynchronous mode, the bus can be used as a generic interface to almost any I/O device. In this design, a standard 8-bit asynchronous mode is used for boot loading and programming the flash memory while a custom interface was designed for interfacing with the input FIFOs. As seen in the schematic, the flash interface uses address space *CE1* and it directly connects to the asynchronous write enable (AWE) and asynchronous output enable (AOE) lines of the DSP. To read and write from the flash memory, the programmer simply sets the CE1 address space for an 8-bit asynchronous interface, then accesses the associated address.

A non-standard asynchronous interface was designed for the input FIFO because the synchronous interface was designed for random access memory (RAM) and the standard asynchronous mode is not appropriate for a synchronous (clocked) FIFO. As seen in the schematic, the asynchronous read enable (ARE) line is used as the FIFO clock signal and the CEO signal is used as a FIFO read enable. The disadvantage to this connection is that a bogus asynchronous read must be repeatedly asserted by the DSP in order to clock the FIFO to update the FIFO flags. This manual clocking must only be performed when the DSP is in the idle state waiting for data to arrive so performance is not compromised in any significant way. During a FIFO read operation, the DSP simply reads a single address in CEO causing the CEO and ARE lines to toggle and the FIFO to output a 32-bit word.

#### XMIF Interface

The XMIF interface is an auxiliary 32-bit bus for interface to standard memory devices including synchronous FIFOs. Up to four devices can be connected to the XMIF without glue logic by using the address spaces mapped to XCE0-XCE3. As seen in the schematic, XCE0 was used to connect to the output FIFOs. The FIFOs connect directly and seamlessly to the XMIF using the XFCLK, XD0-31, and XCE0 signals. The disadvantage to using the XMIF is that the DSP core does not have direct access to it. The only way to access devices on the XMIF is through the use of direct memory access (DMA) transfers. Therefore, the bus is used for large block transfers where the size of the transfer is known (such as the output stage of the data acquisition algorithm) or when an interrupt can signal the DMA system to start/stop transfers.

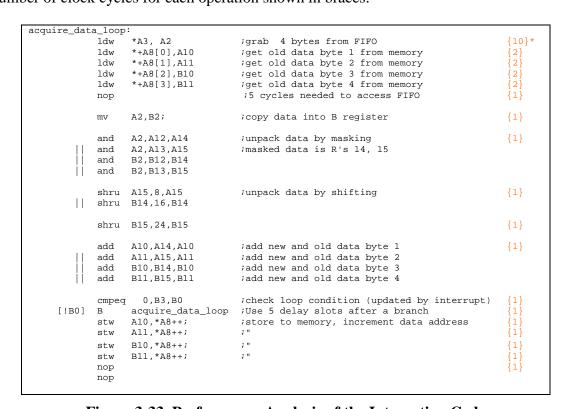

### DSP Boot Configuration

Since the DSP can interface to a variety of memory types, the memory type for the boot ROM must be programmed prior to power up. This is selected via 23-pullup/pulldown resistors on the XMIF bus as shown in Figure 3-25. The boot configuration selected for the averaging card is shown in Table 3-3.

| XMIF pin | Function   | Set to                                           | Value |

|----------|------------|--------------------------------------------------|-------|

| 0-4      | BOOTMODE   | Internal Memory at Address 0, 8 bit ROM bootload | 10110 |

| 5-7      | RESERVED   |                                                  |       |

| 8        | LEND       | Little Endian                                    | 1     |

| 9        | FMOD       | XOE Reserved for a single FIFO in XCE3           | 1     |

| 10       | XARB       | Internal Expansion Bus Arbiter Enabled           | 1     |

| 11       | HMOD       | External Host Interface in Synchronous Mode      | 1     |

| 12       | RWPOL      | XR Signal is Active High                         | 1     |

| 13       | BLPOL      | XBLAST is Active High                            | 1     |

| 14-15    | RESERVED   |                                                  |       |

| 16-18    | MTYPE XCE0 | 32 Bit Synchronous FIFO Interface for XCE0       | 101   |

| 19       | RESERVED   |                                                  |       |

| 20-22    | MTYPE XCE1 | 32 Bit Synchronous FIFO Interface for XCE1       | 101   |

| 23       | RESERVED   |                                                  |       |

| 24-26    | MTYPE XCE2 | 32 Bit Synchronous FIFO Interface for XCE2       | 101   |

| 27       | RESERVED   |                                                  |       |

| 28-30    | MTYPE XCE3 | 32 Bit Synchronous FIFO Interface for XCE3       | 101   |

| 31       | RESERVED   |                                                  |       |

**Table 3-3 Processor Boot Configuration**

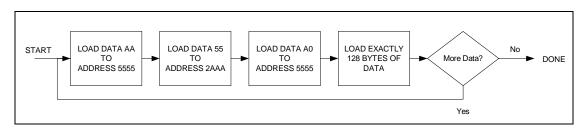

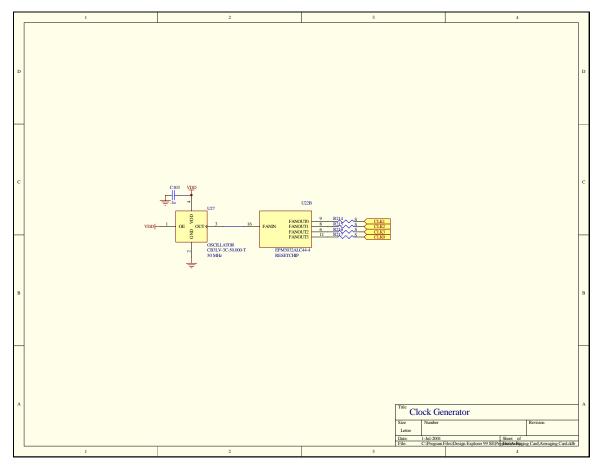

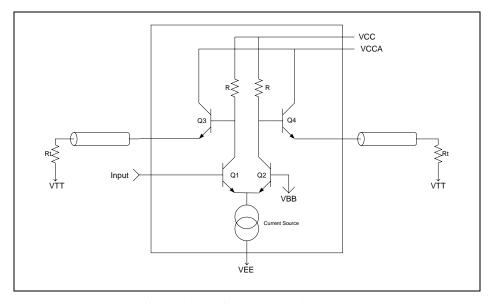

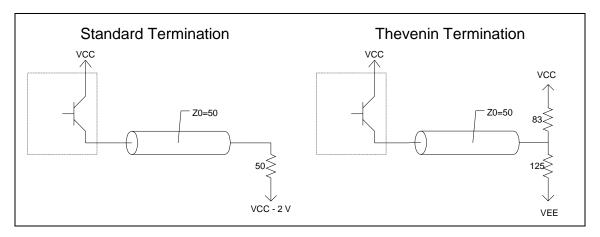

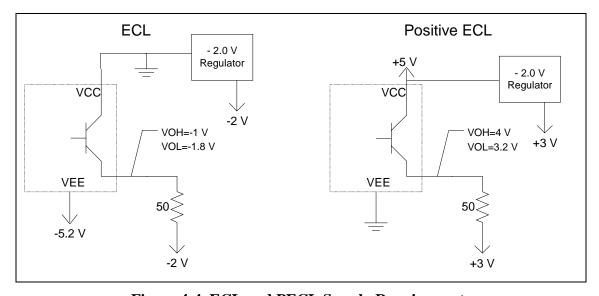

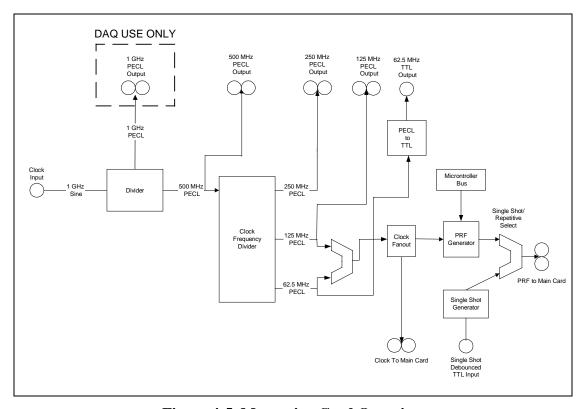

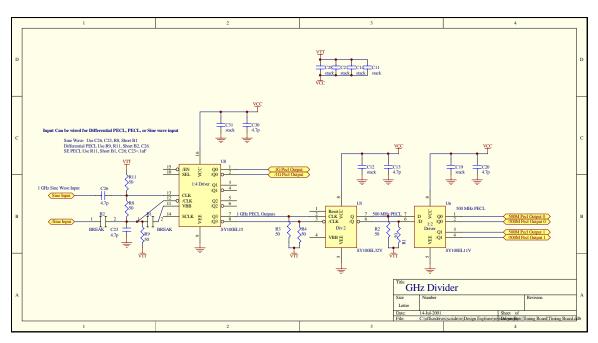

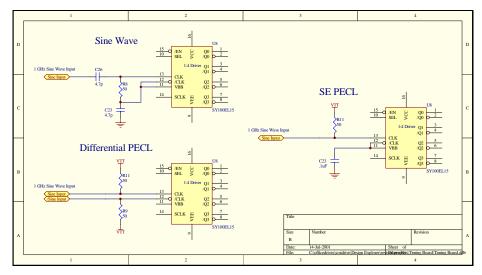

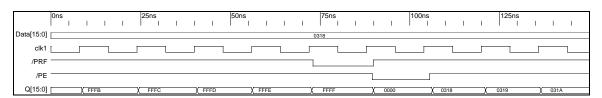

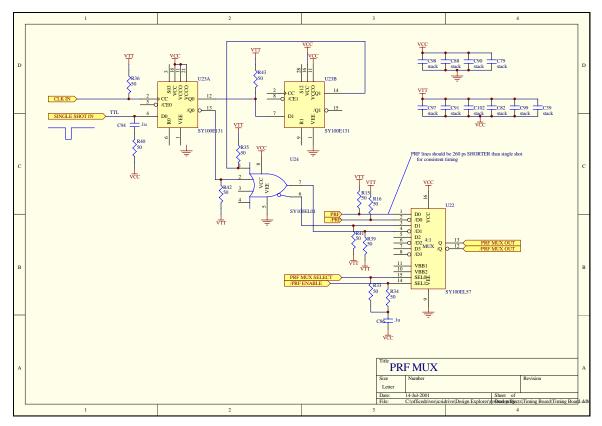

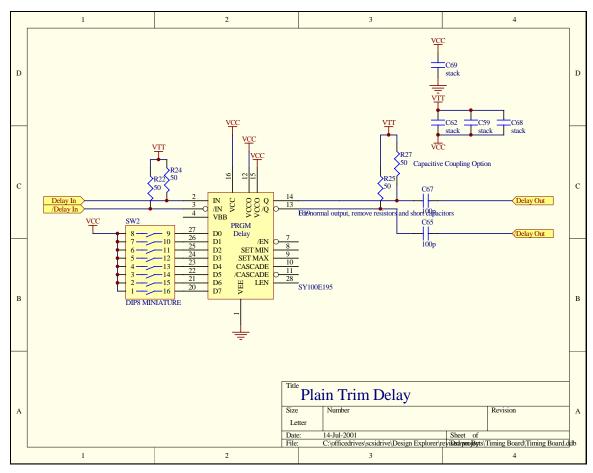

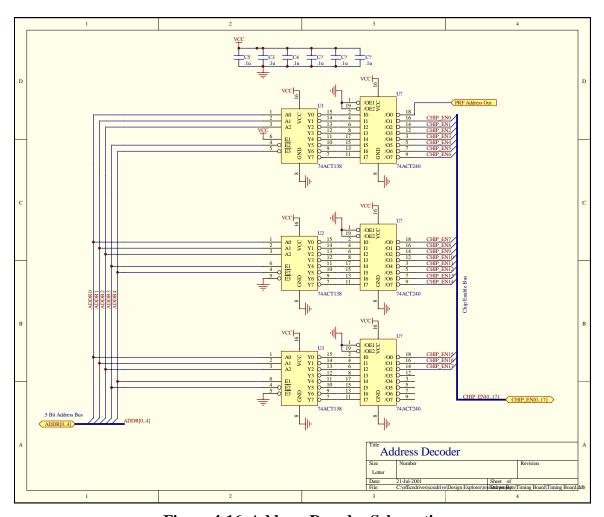

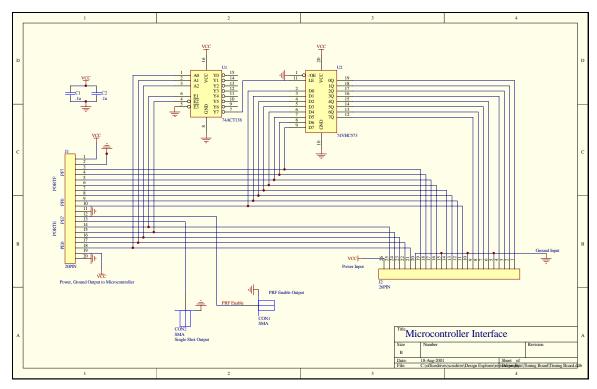

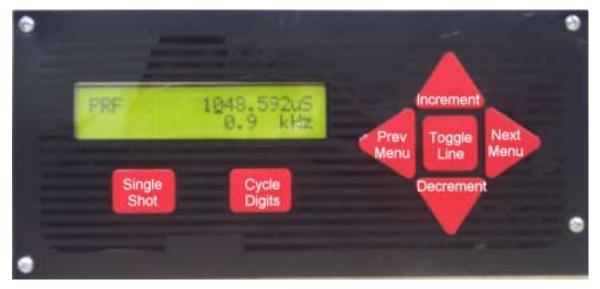

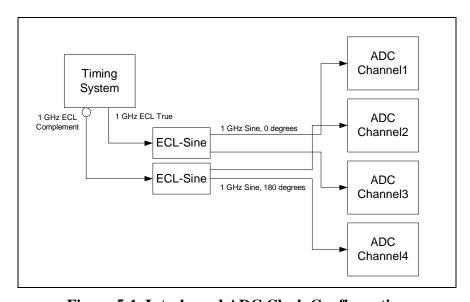

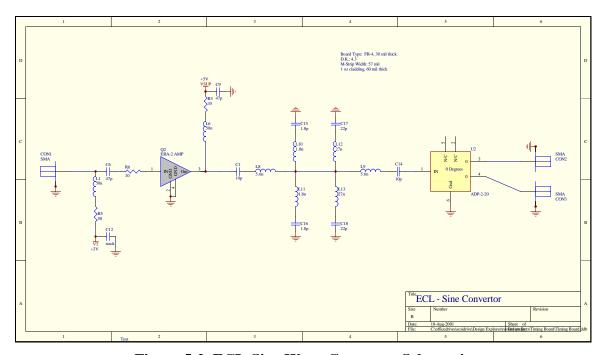

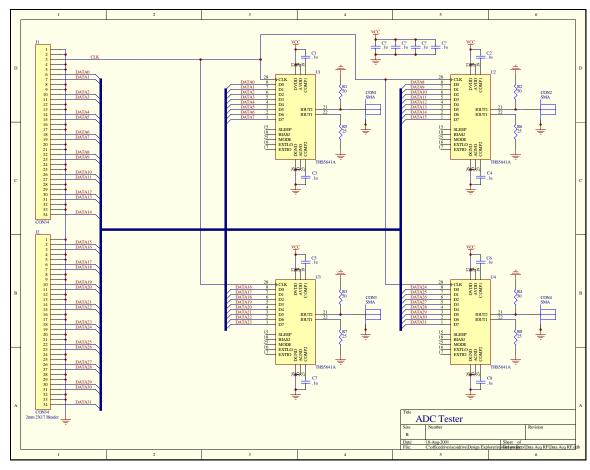

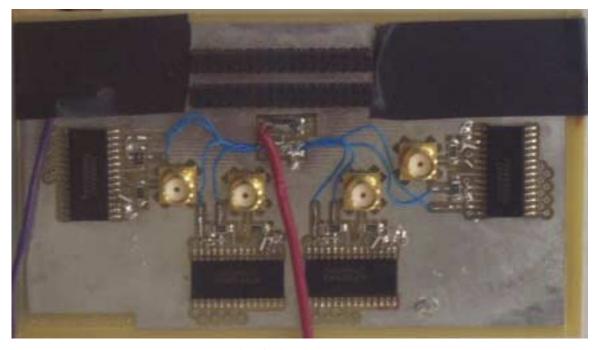

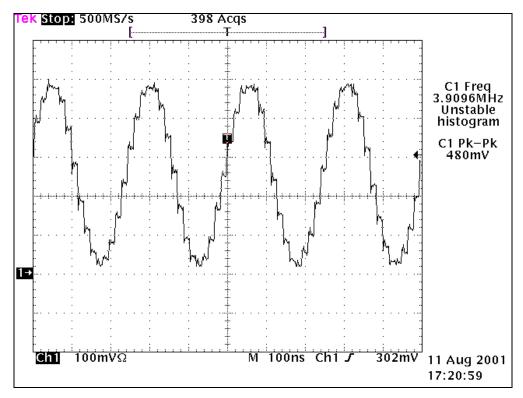

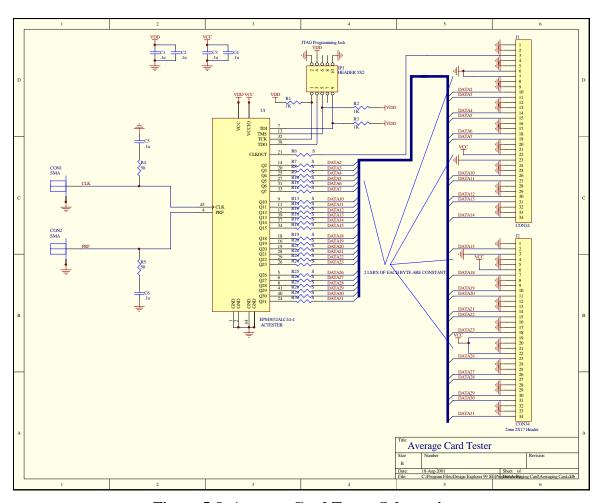

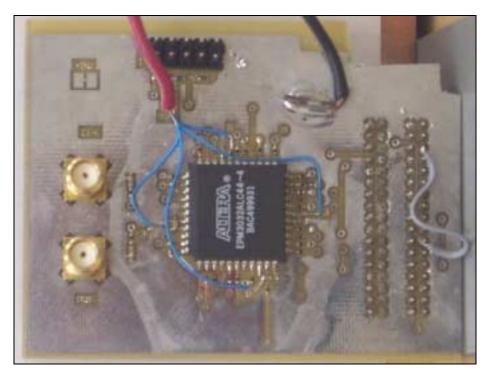

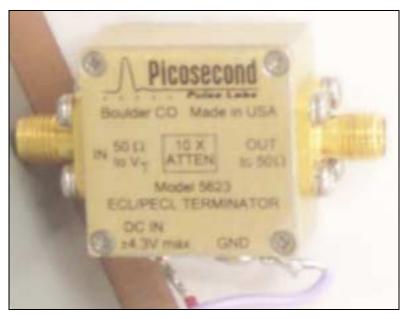

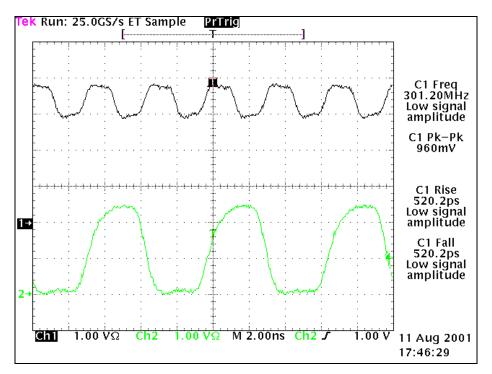

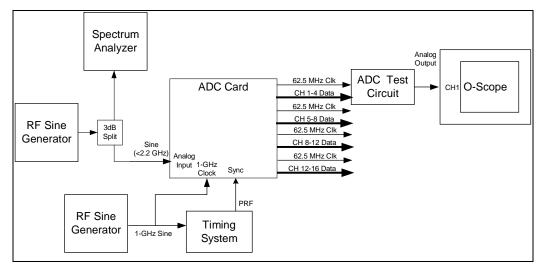

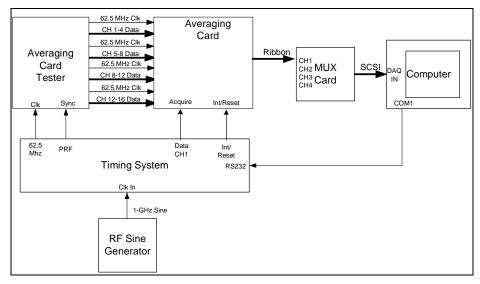

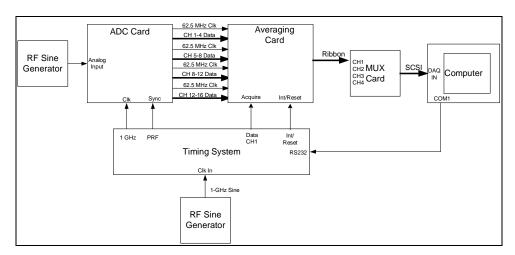

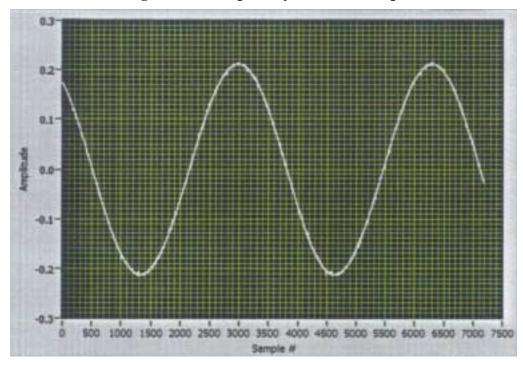

# Flash Memory